cupoftea

Advanced Member level 5

Hi,

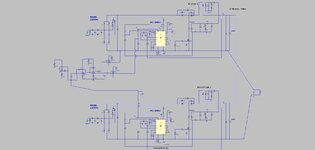

Here is an improvement on the 2 paralleled Average current mode Boost PFCs.

The attached (LTspice and jpeg) is 2 paralleled Boost PFCs. Each is grounded to a slightly different potential, as is often the case in adjacent high current SMPSs.

Anyway, in order to be paralleled, one is Master, and the other is Slave. The Slave has its Current Error Amplifier input as being the same as that of the Master. Obviously each PFC sits on a slightly different ground, so a Diff Amp is needed to pass the Masters Current Error Amplifier input voltage to the Slave.

The attached shows it being done. Can you think of a lower component count way of doing this?

(As you may note, the simulation has been made “quicker-to-run” by forcing a fixed voltage into the Voltage Error Amplifier’s input. In the actual simulation, each PFC would have a feedback divider from the Vout, as normal.)

Here is an improvement on the 2 paralleled Average current mode Boost PFCs.

The attached (LTspice and jpeg) is 2 paralleled Boost PFCs. Each is grounded to a slightly different potential, as is often the case in adjacent high current SMPSs.

Anyway, in order to be paralleled, one is Master, and the other is Slave. The Slave has its Current Error Amplifier input as being the same as that of the Master. Obviously each PFC sits on a slightly different ground, so a Diff Amp is needed to pass the Masters Current Error Amplifier input voltage to the Slave.

The attached shows it being done. Can you think of a lower component count way of doing this?

(As you may note, the simulation has been made “quicker-to-run” by forcing a fixed voltage into the Voltage Error Amplifier’s input. In the actual simulation, each PFC would have a feedback divider from the Vout, as normal.)