anhnha

Full Member level 6

- Joined

- Mar 8, 2012

- Messages

- 322

- Helped

- 4

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 1,298

- Activity points

- 3,684

Hi,

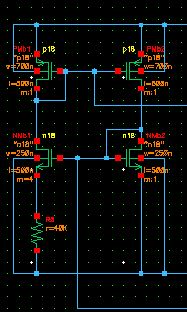

I see that the biasing circuit below is used a lot in op amp design. However, I couldn't find any document explaining how it works. Could anyone tell me some document explain the operating principle of the biasing circuit?

Or could you explain it to me?

Thanks.

I see that the biasing circuit below is used a lot in op amp design. However, I couldn't find any document explaining how it works. Could anyone tell me some document explain the operating principle of the biasing circuit?

Or could you explain it to me?

Thanks.