@kka

Newbie

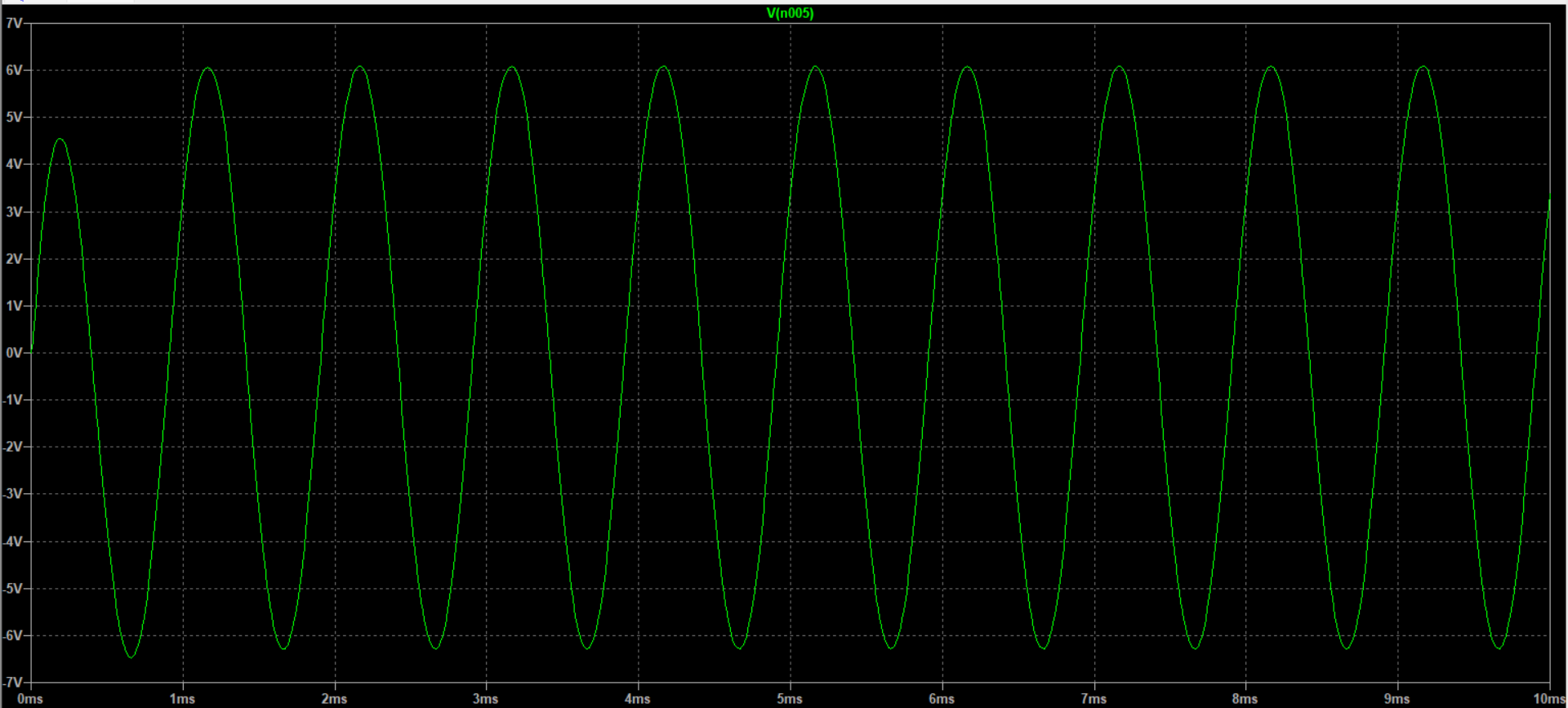

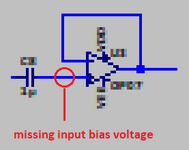

I have to make an audio amplifier with the specifications: Frequency Range: 50 – 20KHz, output voltage : 20mV to 50mV and can be used with 5V supply speaker (8ohm resistance; 0.5W). I made 4 stages first is a preamp stage which has differential amplifier with current mirror load, second stage is a CE amplifier, third is a buffer and 4th is bandpass filter. now i want to add a power amp stage using TIP 31 and 32 power transistors so that I can get required wattage by getting appropriate current gain in this stage but it isn't working. also the output of the 4th stage is 6V(which is fine because designing it on hardware will reduce the voltage gain anyways so I put a little higher gain) but it has a dc offset also there is distortion(uneven) where the sinusoid is of greater amplitude on negative side whereas it is exactly 6 on the positive side. I'm attaching the ltspice file which contains my design and also the image of the output.