aliraza786

Full Member level 4

- Joined

- Nov 10, 2009

- Messages

- 210

- Helped

- 14

- Reputation

- 28

- Reaction score

- 14

- Trophy points

- 1,298

- Location

- Lahore, Pakistan, Pakistan

- Activity points

- 2,914

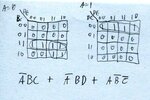

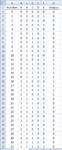

A digital circuit which detect when input binary number is from 9 to 19 range

i wana design a circuit which can detect when the input is greater then 9 and up to 19 ......i dnt know how to use k map for five variable....can any one help me how can i use CAD tools to make such types of circuits instead of usng k map..becuse a professional approch is CAD tools..........

i wana design a circuit which can detect when the input is greater then 9 and up to 19 ......i dnt know how to use k map for five variable....can any one help me how can i use CAD tools to make such types of circuits instead of usng k map..becuse a professional approch is CAD tools..........