mag5

Newbie level 3

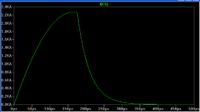

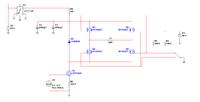

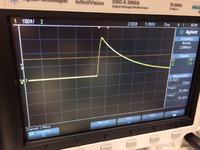

Heres a simplified circuit, that inconsistently blows the mosfet. Charging the cap with a 50V 2A limited supply, and firing 5ms pulses at a period of 10s. I sense the current at the 0.001mOhm shunt. What am I doing wrong?

https://obrazki.elektroda.pl/4241127500_1410385744.png

https://obrazki.elektroda.pl/4241127500_1410385744.png