Ata_sa16

Full Member level 6

- Joined

- Mar 29, 2016

- Messages

- 343

- Helped

- 59

- Reputation

- 118

- Reaction score

- 58

- Trophy points

- 28

- Location

- Milky Way Galaxy, 179° 56′ 39.4″

- Activity points

- 2,221

Hi all,

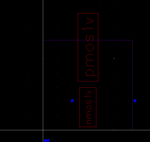

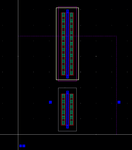

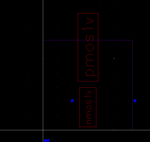

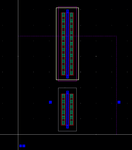

I've confronted a problem in Cadence layout design. I started with a simple inverter layout. The problem is, I cannot fit 2 transistors inside the selection box and cant stretch it either.

Can anyone help me with this? :bang::bang::bang::bang::bang::bang:

they should be inside that purple box !!

(I know I can use fingers or multipliers. I just want to know if there is another solution ... ?)

I've confronted a problem in Cadence layout design. I started with a simple inverter layout. The problem is, I cannot fit 2 transistors inside the selection box and cant stretch it either.

Can anyone help me with this? :bang::bang::bang::bang::bang::bang:

they should be inside that purple box !!

(I know I can use fingers or multipliers. I just want to know if there is another solution ... ?)