tompham

Full Member level 2

- Joined

- May 29, 2010

- Messages

- 133

- Helped

- 29

- Reputation

- 60

- Reaction score

- 29

- Trophy points

- 1,308

- Location

- usa

- Activity points

- 2,066

Hi all

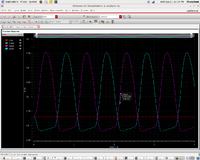

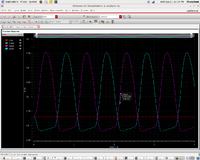

Im desinging 2 stage fully differential opamp with continous cmfb. My design using smic18mmrf with VDD=3.3v and input cm = output cm = 1.65v. I test transient with apply sin wave 20uV peak to peak

to see how output behave. From the waveform (see attached) , the output distortion at below output common mode. I have hard time to figure the problem even the opamp has good output swing. Anyone can help me with this. Thanks a lot

Im desinging 2 stage fully differential opamp with continous cmfb. My design using smic18mmrf with VDD=3.3v and input cm = output cm = 1.65v. I test transient with apply sin wave 20uV peak to peak

to see how output behave. From the waveform (see attached) , the output distortion at below output common mode. I have hard time to figure the problem even the opamp has good output swing. Anyone can help me with this. Thanks a lot