serhannn

Member level 4

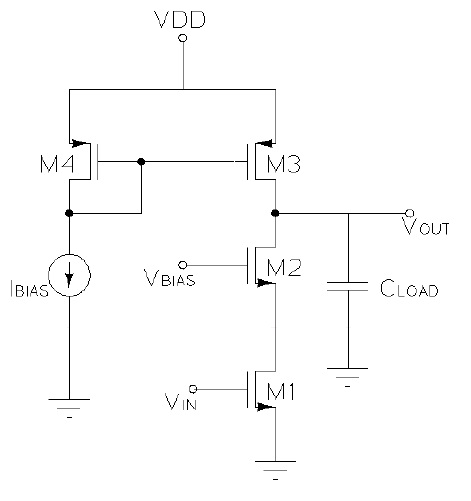

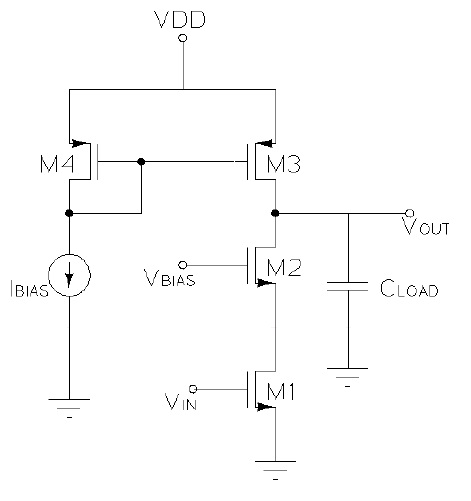

I need to design a cascode amplifier. Specifications are Vdd=3.3V, Power Consumption= 1mW, Gain=50 V/V, Output Swing rate 1.3V (Vmax=2.5, Vmin=1.2) and slew rate with a 10pF load should be 10V/μs or greater. Figure is included.

My problem is, I get a much lower slew rate (even lower than 1 V/μs) when I design for a 50 V/V gain and a power consumption less than 1 mW. I know I should increase the bias current to meet that but when I do this, the power consumption obviously increases a lot and also with a higher bias current I can't seem to get the desired gain. What should be the design approach here? I use a bias current of 75μA. Should I start with a much higher one and arrange for the slew rate first and then worry about the gain and swing range? What are your advices?

Thank you.

My problem is, I get a much lower slew rate (even lower than 1 V/μs) when I design for a 50 V/V gain and a power consumption less than 1 mW. I know I should increase the bias current to meet that but when I do this, the power consumption obviously increases a lot and also with a higher bias current I can't seem to get the desired gain. What should be the design approach here? I use a bias current of 75μA. Should I start with a much higher one and arrange for the slew rate first and then worry about the gain and swing range? What are your advices?

Thank you.