sys_eng

Full Member level 4

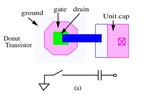

In the book it says

Because the drain area of the donut transistor is shared by the gates in all four sides, the parasitic drain capacitance is

reduced to minimum,

why drain area surrounded by gate has minimum drain capacitance?

Cgd capacitance between gate and drain , if the drain surrounded by gate that means more drain-gate overlap therefore increase the capacitance instead of minimizes it. It doesn't make sense.

Because the drain area of the donut transistor is shared by the gates in all four sides, the parasitic drain capacitance is

reduced to minimum,

why drain area surrounded by gate has minimum drain capacitance?

Cgd capacitance between gate and drain , if the drain surrounded by gate that means more drain-gate overlap therefore increase the capacitance instead of minimizes it. It doesn't make sense.