exceeder88

Newbie level 2

Hi, im new to verilog. im trying to understand a code provided by xilink to create a multiplexer. the code is as follows:

the ".I0" part, what kind of operator is that? didnt find any reference to "dot" operator.

Code:

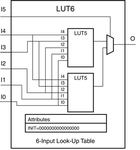

LUT6 #(

.INIT (64'h0000000F003355FF))

selection0_lut(

.I0 (data_in[0]),

.I1 (data_in[1]),

.I2 (data_in[2]),

.I3 (sel[0]),

.I4 (sel[1]),

.I5 (sel[2]),

.O (muxcy_sel[0]));the ".I0" part, what kind of operator is that? didnt find any reference to "dot" operator.