loxly

Junior Member level 3

- Joined

- Mar 16, 2012

- Messages

- 29

- Helped

- 6

- Reputation

- 12

- Reaction score

- 6

- Trophy points

- 1,283

- Location

- Zagreb, Croatia

- Activity points

- 1,530

I have some questions regarding to design of RCD circuit of flyback converter.

Converter specifications:

input: 50 V

output 100 V, 100 W (100 Ohm resistance)

Output current 1 A

transformer current ripple 2A (CCM)

output capacitor 680 uF, 100 V

Turns ratio: 1

Duty cycle: 0.67

The problem is that when I'm using calculated R and C values ( according to some equations I've found 10k, 47 nF) , I still get quite large (above kV) voltage spikes on my Simplorer model simulation. But when I use a combination of quite larger value for C (47 or 150 uF) and R (33k, for smaller losses) everything seems ok on the simulation! (spikes are reasonable).

I've been searching a lot, and I haven't found anywhere that someone uses RCD snubber capacitor much larger than 47 nF!

It's maybe because of large output capacitor, but I can't change it. It is already on the board where we constructed universal non-isolated DC converter.

Are there any drawbacks of using such a large capacitor in snubber circuit? What could cause this?

I don't have anything against using such a big capacitor if you don't

I don't have any experience in flyback design, so I'm asking you.

Thank you for your help

Lovro

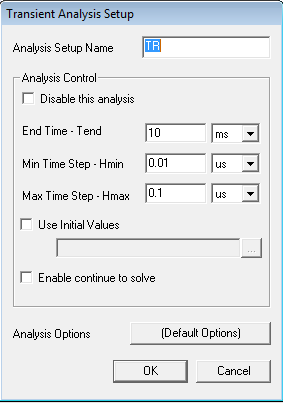

P.S. I have modeled flyback transformer in PExpert and add model in simplorer, so it's pretty accurate. I can even send you my flyback Simplorer model if needed!

Converter specifications:

input: 50 V

output 100 V, 100 W (100 Ohm resistance)

Output current 1 A

transformer current ripple 2A (CCM)

output capacitor 680 uF, 100 V

Turns ratio: 1

Duty cycle: 0.67

The problem is that when I'm using calculated R and C values ( according to some equations I've found 10k, 47 nF) , I still get quite large (above kV) voltage spikes on my Simplorer model simulation. But when I use a combination of quite larger value for C (47 or 150 uF) and R (33k, for smaller losses) everything seems ok on the simulation! (spikes are reasonable).

I've been searching a lot, and I haven't found anywhere that someone uses RCD snubber capacitor much larger than 47 nF!

It's maybe because of large output capacitor, but I can't change it. It is already on the board where we constructed universal non-isolated DC converter.

Are there any drawbacks of using such a large capacitor in snubber circuit? What could cause this?

I don't have anything against using such a big capacitor if you don't

I don't have any experience in flyback design, so I'm asking you.

Thank you for your help

Lovro

P.S. I have modeled flyback transformer in PExpert and add model in simplorer, so it's pretty accurate. I can even send you my flyback Simplorer model if needed!