arkadiusz.gibes

Newbie level 4

Hello everyone

I'm playing with some kind of 3 phase motor controller and i have issue with high side mosfet driver. My circuit seems to work well until HV voltage rail will be increased to some level.

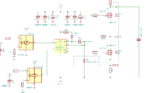

When it reaches about 150V the high side drivers are blowing up. I made a tests with no inductive load and everything was working correctly. The tests that i made were with 240V DC on power rail. The desired working voltage is 200V. My high side driver is IR25604. It's just a simple driver without any cool features. The device is operating with 50kHz pwm. Does anyone could help me with analysis of this issue ? The interesting thing is that my mosfets are still alive after IR25604 gose down. In attachments you find schematics and board layout. I presume that issue may be because in bad bootstrap or filtering ? The motor type is 3f BLDC around 100W.

Best Regards

Arkadiusz

I'm playing with some kind of 3 phase motor controller and i have issue with high side mosfet driver. My circuit seems to work well until HV voltage rail will be increased to some level.

When it reaches about 150V the high side drivers are blowing up. I made a tests with no inductive load and everything was working correctly. The tests that i made were with 240V DC on power rail. The desired working voltage is 200V. My high side driver is IR25604. It's just a simple driver without any cool features. The device is operating with 50kHz pwm. Does anyone could help me with analysis of this issue ? The interesting thing is that my mosfets are still alive after IR25604 gose down. In attachments you find schematics and board layout. I presume that issue may be because in bad bootstrap or filtering ? The motor type is 3f BLDC around 100W.

Best Regards

Arkadiusz