EEPuppyPuppy

Junior Member level 3

SRAM RC Extraction Simulation Does NOT Match Schematic Simulation

Hi, really hope someone could help me.

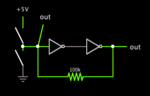

About the circuit" I am doing an in-memory calculation structure very similar to SRAM which has both write and read.

The writing process writes data into the structure; the reading process needs some inputs and will do some performance with the stored data inside the structure then generates some outputs.

Problems: The simulation of the schematic netlist works well; however, after layout and RC extraction, it does not work properly. I use Cadence Virtuoso with Calibre PEX to do the RC extraction.

The problems typically happen when the RC extraction contains R values (eg. R+C+CC or R+C), the stored value in the cell becomes unstable and might flip its value (eg. In the reading process, previously-stored 0 inside the cell in the writing process jitters and end up with 1). And of course, the output is also wrong. Ideally, the stored value should not change during the reading process.

If I do RC extraction without R (C+CC), the output is always correct, the stored values maintain the values, just like what I got from the schematic netlist simulation.

Initially, I thought this might because the resistances are too large. But I did not get any luck after increase the metal width as wide as possible.

Later I noticed that in the tech documentation, it mentions if the oxide is too long when carrying signals, the signals might not be stable. So I cut those suspect long oxide into small pieces.

Unfortunately, after trying both of these, the RC extraction circuit still shows a very similar wrong behavior. The output is wrong. The jitters on the stored value get smoother but the stored value still cannot hold itself.

Could anyone give me some suggestions about what I should do next? Any debug mechanism I could possibly use? Anyone had a similar problem before and got it solved?

Thank you very much.

Hi, really hope someone could help me.

About the circuit" I am doing an in-memory calculation structure very similar to SRAM which has both write and read.

The writing process writes data into the structure; the reading process needs some inputs and will do some performance with the stored data inside the structure then generates some outputs.

Problems: The simulation of the schematic netlist works well; however, after layout and RC extraction, it does not work properly. I use Cadence Virtuoso with Calibre PEX to do the RC extraction.

The problems typically happen when the RC extraction contains R values (eg. R+C+CC or R+C), the stored value in the cell becomes unstable and might flip its value (eg. In the reading process, previously-stored 0 inside the cell in the writing process jitters and end up with 1). And of course, the output is also wrong. Ideally, the stored value should not change during the reading process.

If I do RC extraction without R (C+CC), the output is always correct, the stored values maintain the values, just like what I got from the schematic netlist simulation.

Initially, I thought this might because the resistances are too large. But I did not get any luck after increase the metal width as wide as possible.

Later I noticed that in the tech documentation, it mentions if the oxide is too long when carrying signals, the signals might not be stable. So I cut those suspect long oxide into small pieces.

Unfortunately, after trying both of these, the RC extraction circuit still shows a very similar wrong behavior. The output is wrong. The jitters on the stored value get smoother but the stored value still cannot hold itself.

Could anyone give me some suggestions about what I should do next? Any debug mechanism I could possibly use? Anyone had a similar problem before and got it solved?

Thank you very much.