T

treez

Guest

Hi

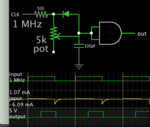

We have pulses which we need to delay by some approx. 280ns, and indeed we need to make the pulses shorter, again by some approx. 280ns

The attached (ltspice sim and pdf) show two circuits which could possibly achieve this.

Do you agree that the top circuit, which uses a logic buffer IC, is not workable in reality due to the high output impedance of the buffer? The SN74LVC1G17 datasheet suggests that at 5vin, its output resistance is 5V/0.032A = 156 Ohms…this is too high in this circuit.

Due to this, a FET gate driver IC must instead be used, as in the bottom circuit…(due to its definite low output resistance) ….would you agree?

SN74LVC1G17 logic buffer IC

https://www.ti.com/lit/ds/symlink/sn74lvc1g17.pdf

We have pulses which we need to delay by some approx. 280ns, and indeed we need to make the pulses shorter, again by some approx. 280ns

The attached (ltspice sim and pdf) show two circuits which could possibly achieve this.

Do you agree that the top circuit, which uses a logic buffer IC, is not workable in reality due to the high output impedance of the buffer? The SN74LVC1G17 datasheet suggests that at 5vin, its output resistance is 5V/0.032A = 156 Ohms…this is too high in this circuit.

Due to this, a FET gate driver IC must instead be used, as in the bottom circuit…(due to its definite low output resistance) ….would you agree?

SN74LVC1G17 logic buffer IC

https://www.ti.com/lit/ds/symlink/sn74lvc1g17.pdf