T

treez

Guest

Hello

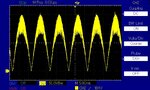

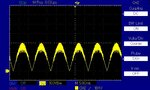

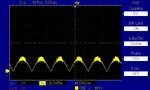

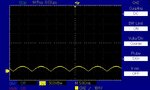

I was scoping the Primary , Post rectifier DC Bus in a 100W, 240VAC, offline PFC’d Flyback to see what the voltage ripple was like on this rail.

As you can see, at the mains peak, there is a lot of noise at the peak of the waveform that makes the measurement impossible.

The blue waveforms were done with a x10 scope probe (with a dangling ground clip) with its lead wound in three turns round a ferrite torroid. The yellow waveforms are done with a diff probe.

I obviously need a ten times coaxial probe without the dangling ground clip.

Do you know of one?...or must I do the old trick of wrapping wire round the ground barrel of the probe?

I was scoping the Primary , Post rectifier DC Bus in a 100W, 240VAC, offline PFC’d Flyback to see what the voltage ripple was like on this rail.

As you can see, at the mains peak, there is a lot of noise at the peak of the waveform that makes the measurement impossible.

The blue waveforms were done with a x10 scope probe (with a dangling ground clip) with its lead wound in three turns round a ferrite torroid. The yellow waveforms are done with a diff probe.

I obviously need a ten times coaxial probe without the dangling ground clip.

Do you know of one?...or must I do the old trick of wrapping wire round the ground barrel of the probe?

Attachments

-

diff probe _50v per div.jpg134.7 KB · Views: 140

diff probe _50v per div.jpg134.7 KB · Views: 140 -

diff probe _100v per div.jpg120.2 KB · Views: 136

diff probe _100v per div.jpg120.2 KB · Views: 136 -

diff probe _200v per div.jpg111.7 KB · Views: 140

diff probe _200v per div.jpg111.7 KB · Views: 140 -

diff probe _500v per div.jpg104.7 KB · Views: 140

diff probe _500v per div.jpg104.7 KB · Views: 140 -

scope probe _50v per div.jpg115.4 KB · Views: 143

scope probe _50v per div.jpg115.4 KB · Views: 143 -

scope probe _100v per div.jpg108 KB · Views: 144

scope probe _100v per div.jpg108 KB · Views: 144 -

scope probe _200v per div.jpg108.7 KB · Views: 149

scope probe _200v per div.jpg108.7 KB · Views: 149