turtlewang

Member level 2

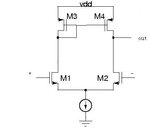

hello everybody, now i am designing a simple OPAMP for bandgap reference. I choose the following OPAMP. How can I calculate the random input-referred offset voltage? What I want is to use some equations to hand calculate the size of the input transistor, then use the calculated transistor for simulation e.g. Monte Carlo simulation.

Are there any documents describing the equation?

Thanks

Are there any documents describing the equation?

Thanks