naalald

Full Member level 4

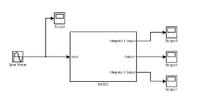

simulink discrete-time integrator problem

Hi,

I want to simulate a DS modulator in simulink. When I use,

Input frequency = 85/8192

Sample time = 1

like the values in the Schreier toolbox, everything is ok. But when I use,

Input frequency = 85

Sample time = 1/8192

The modulator does not work. I guess the problem is something to do with the simulink and the blocks, which may ignore or round the numbers when they are so small. I set the sample time for one block and for other blocks I set -1 for inherited.

Any suggestions?

Hi,

I want to simulate a DS modulator in simulink. When I use,

Input frequency = 85/8192

Sample time = 1

like the values in the Schreier toolbox, everything is ok. But when I use,

Input frequency = 85

Sample time = 1/8192

The modulator does not work. I guess the problem is something to do with the simulink and the blocks, which may ignore or round the numbers when they are so small. I set the sample time for one block and for other blocks I set -1 for inherited.

Any suggestions?