ckseu

Newbie level 4

when are rhp zero formed

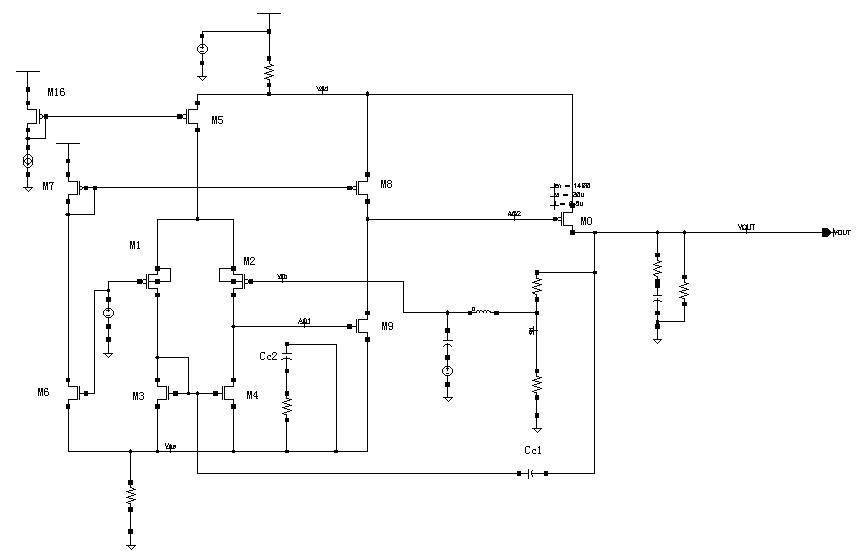

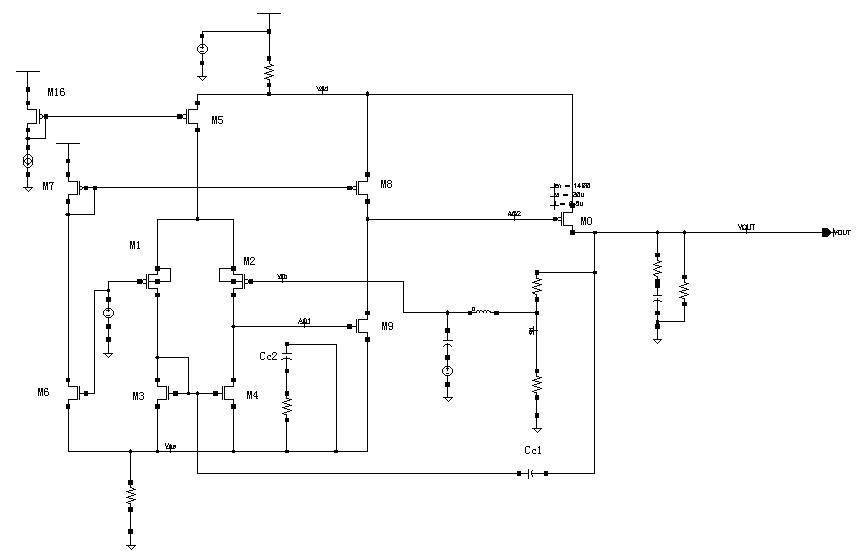

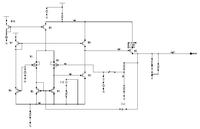

This structure is built follow the Rincon-Mora Enhanced Miller Compensation method

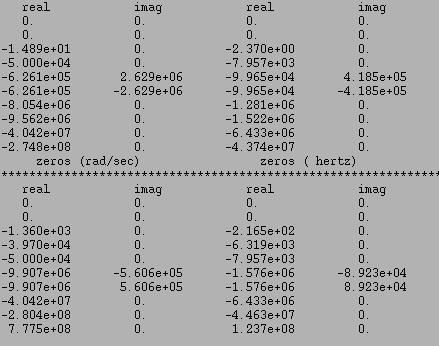

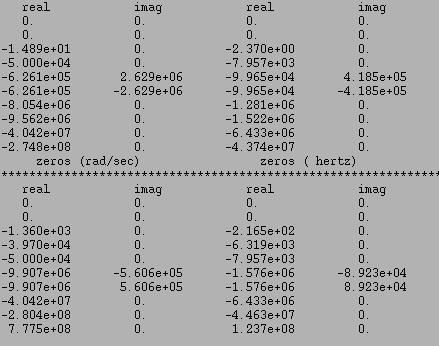

In his paper, the structure can pull two poles as far as possible. This loop can be compensated stably, But There is a zero=-2.165e+02, which I can’t find where it comes form. It seems too low. Cc2 have no effect to this zero. Cc1=10pF.

I hope to get help from the family of EDAboard. Any detail you want to know about the circuit please ask me.

Thanks!

There are two papers may be help :

Active capacitor multiplier in Miller-compensated circuits:

Dual-loop feedback for fast low dropout regulators

This structure is built follow the Rincon-Mora Enhanced Miller Compensation method

In his paper, the structure can pull two poles as far as possible. This loop can be compensated stably, But There is a zero=-2.165e+02, which I can’t find where it comes form. It seems too low. Cc2 have no effect to this zero. Cc1=10pF.

I hope to get help from the family of EDAboard. Any detail you want to know about the circuit please ask me.

Thanks!

There are two papers may be help :

Active capacitor multiplier in Miller-compensated circuits:

Dual-loop feedback for fast low dropout regulators

Last edited by a moderator: