wwfeldman

Advanced Member level 4

I want to use a Cypress (Infineon) Kit-059 to control a 16x16 cross-point switch, Analog Devices AD75019, using the SPI master component. The AD75019 takes 256 bits of serial data clocked in a CPHA= 0, CPOL=0 format. It then clocks the 256 bits in parallel to control the switches.

I am examining SPIM_Example Project 1.10 to get an understanding of using am SPI as a master. I am also looking at documentation component data sheets Serial Peripheral Interface (SPI) Master 2.50, Direct Memory Access 1.70, ap notes AN52705 and AN84810, and the data sheet for the AD75019.

I am tied down to the AD75019, as it is the only cross-point switch I have found with the appropriate voltage range. It gets a 256 bit data stream to set the 256 switches.

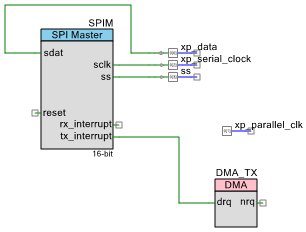

This is the portion of the TopDesign in PSoC Creator with the SPI Master

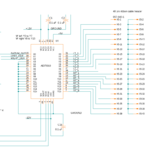

This is the pertinent portion of the crosspoint switch circuit, from Fusion 360 electronics:

in the SPIM Example, main.c:

CyDmaChEnable(txChannel, STORE_TD_CFG_ONCMPLT);

while (0u == (SPIM_ReadTxStatus() & SPIM_STS_SPI_DONE))

{

}

what I get, and do not get:

Does enabling the DMA channel cause it to transmit? If not, what does?

Where can I find the various codes, like STORE_TD_CFG_ONCMPLT, and what they mean/do?

The while loop continues through each 8 bytes of the buffer, until both SPIM_ReadTxStatus() and SPIM_STS_SPI_DONE are 1.

other items:

I am using the DMA because I need to transmit 256 bits. The SPI does 16 bit bursts, so I need to string together 16 transmit descriptors.

In operation, the crosspoint switch looks like an analog shift register, for at least 10 steps. (nothing, 8 steps, and nothing again)

Since I only want to transmit the data, as the cross-point switch is not an SPI device, but it does take serial data clocked in, in the same format as SPI ( CPHA= 0, CPOL=0 format.). I don't need the MISO input. The component sheet says it needs to be connected, but to what?

Is it okay to ground it, or tie it high?

Data lines selection "Bi-directional" looks more like what I need, and is what is in the schematic above: DATA and CLOCK.

Since there is only one SPI (not quite slave) device, I don't need the Slave Select, and plan to leave it unconnected.

The other question I currently have has to do specifically with the operation of the SPIM Example:

At the beginning of main.c, the data buffers are declared:

/* Data buffers */

uint8 txBuffer [BUFFER_SIZE] = {0x0u, 0x01u, 0x02u, 0x03u, 0x04u, 0x05u, 0x06u, 0x07u};

uint8 rxBuffer[BUFFER_SIZE];

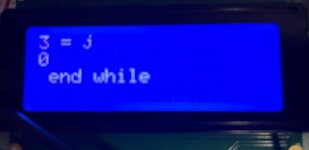

How does the information in the transmit buffer (looks like octal(?) or hex(?) bytes 0 through 7) lead to the expected results per the SPIM example pdf? It is clear that Master RX data: is written directly to the LCD display.

(from the SPIM pdf file

Expected Results

The LCD should display:

Master Rx data:

090A0B0C0D0E0F

( I am thinking there is a disconnect between whoever did the example in PSoC Creator, and whoever wrote the .pdf)

I am examining SPIM_Example Project 1.10 to get an understanding of using am SPI as a master. I am also looking at documentation component data sheets Serial Peripheral Interface (SPI) Master 2.50, Direct Memory Access 1.70, ap notes AN52705 and AN84810, and the data sheet for the AD75019.

I am tied down to the AD75019, as it is the only cross-point switch I have found with the appropriate voltage range. It gets a 256 bit data stream to set the 256 switches.

This is the portion of the TopDesign in PSoC Creator with the SPI Master

This is the pertinent portion of the crosspoint switch circuit, from Fusion 360 electronics:

in the SPIM Example, main.c:

CyDmaChEnable(txChannel, STORE_TD_CFG_ONCMPLT);

while (0u == (SPIM_ReadTxStatus() & SPIM_STS_SPI_DONE))

{

}

what I get, and do not get:

Does enabling the DMA channel cause it to transmit? If not, what does?

Where can I find the various codes, like STORE_TD_CFG_ONCMPLT, and what they mean/do?

The while loop continues through each 8 bytes of the buffer, until both SPIM_ReadTxStatus() and SPIM_STS_SPI_DONE are 1.

other items:

I am using the DMA because I need to transmit 256 bits. The SPI does 16 bit bursts, so I need to string together 16 transmit descriptors.

In operation, the crosspoint switch looks like an analog shift register, for at least 10 steps. (nothing, 8 steps, and nothing again)

Since I only want to transmit the data, as the cross-point switch is not an SPI device, but it does take serial data clocked in, in the same format as SPI ( CPHA= 0, CPOL=0 format.). I don't need the MISO input. The component sheet says it needs to be connected, but to what?

Is it okay to ground it, or tie it high?

Data lines selection "Bi-directional" looks more like what I need, and is what is in the schematic above: DATA and CLOCK.

Since there is only one SPI (not quite slave) device, I don't need the Slave Select, and plan to leave it unconnected.

The other question I currently have has to do specifically with the operation of the SPIM Example:

At the beginning of main.c, the data buffers are declared:

/* Data buffers */

uint8 txBuffer [BUFFER_SIZE] = {0x0u, 0x01u, 0x02u, 0x03u, 0x04u, 0x05u, 0x06u, 0x07u};

uint8 rxBuffer[BUFFER_SIZE];

How does the information in the transmit buffer (looks like octal(?) or hex(?) bytes 0 through 7) lead to the expected results per the SPIM example pdf? It is clear that Master RX data: is written directly to the LCD display.

(from the SPIM pdf file

Expected Results

The LCD should display:

Master Rx data:

090A0B0C0D0E0F

( I am thinking there is a disconnect between whoever did the example in PSoC Creator, and whoever wrote the .pdf)