parth22

Member level 4

Hi all,

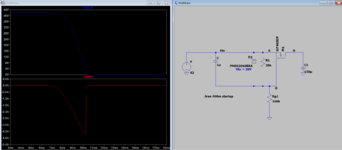

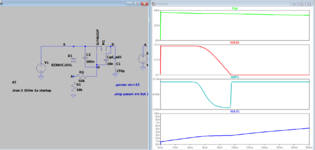

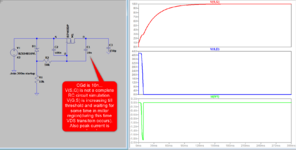

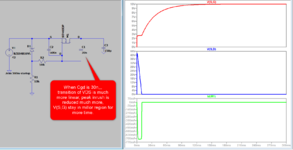

I have query regarding PMOS gate voltage. In the below image, everything is fine but if I change the supply voltage then VGS is changes and linear region of PMOS is going to be change.

Can anyone give suggestion how to control the gate voltage so it works in linear region for all supply voltage range (25-42).

Thanks.

I have query regarding PMOS gate voltage. In the below image, everything is fine but if I change the supply voltage then VGS is changes and linear region of PMOS is going to be change.

Can anyone give suggestion how to control the gate voltage so it works in linear region for all supply voltage range (25-42).

Thanks.