AMSA84

Advanced Member level 2

- Joined

- Aug 24, 2010

- Messages

- 577

- Helped

- 8

- Reputation

- 16

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Iberian Peninsula

- Activity points

- 6,178

Hi guys,

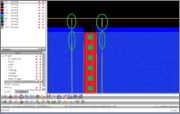

I am facing a problem here. You can see in the picture bellow:

I have join the drain and source of two transistor (diff. pair) in a interdigitated fashion. When I did this, cadence started to show a yellow warning.

I know that one can remove that but I don't remember how.

Does anyone knows?

Regards.

I am facing a problem here. You can see in the picture bellow:

I have join the drain and source of two transistor (diff. pair) in a interdigitated fashion. When I did this, cadence started to show a yellow warning.

I know that one can remove that but I don't remember how.

Does anyone knows?

Regards.

Last edited by a moderator: