lovaraju.ch

Newbie level 6

Dear all,

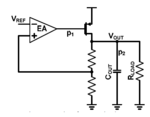

I am designing a low dropout regulator for 1 mA to 100 mA of load current. when the load current is 1 mA the pass transistor (pmos) is going into the subthreshold region and due to this, overshoot and undershoot are increased . so could you please tell me how to avoid subthreshold operation of pass transistor at 1 mA of load current.

waiting for your valueble reply

thanks...

I am designing a low dropout regulator for 1 mA to 100 mA of load current. when the load current is 1 mA the pass transistor (pmos) is going into the subthreshold region and due to this, overshoot and undershoot are increased . so could you please tell me how to avoid subthreshold operation of pass transistor at 1 mA of load current.

waiting for your valueble reply

thanks...