coolsummer

Junior Member level 3

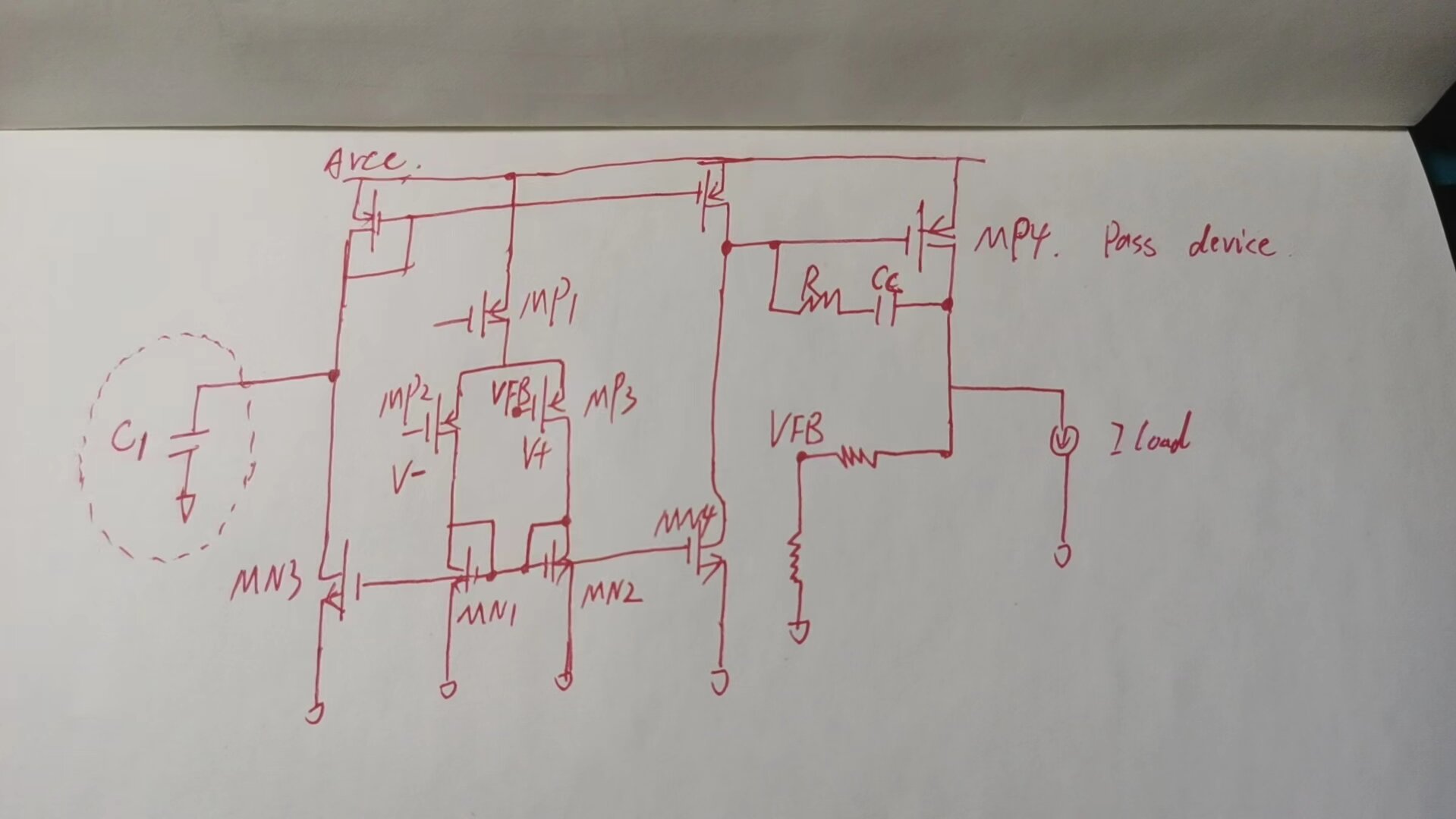

Hello, I have met a LDO circuit as shown, the first stage is a symmetric op and MP4 is the pass device. With cap C1 added, the PSR has significant improvement, but I'm confused on how to choose C1's Capacitance, I simulate it when C1 is too large or small, it has no effect. I simulate it with 1V ac on AVCC and plot output node‘s response. So, What's the principle of this method and how to choose C1?Is there any paper about it?