r.mirtaji

Junior Member level 3

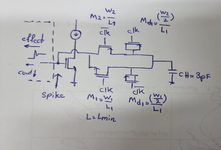

I designed a circuit and I want to sample a voltage at a node(vgs) Corresponding to the previous stage in the period of the time and keep it for a short time

when I use the complementary switch with dummy due to clock-feedthrough it creates spike in transition clock in the previous stage and i have to choose big CH

how can i cancel these spike

what kind of model switch (complementary, bootstrapped,... ) are suitable for sample and hold circuit

when I use the complementary switch with dummy due to clock-feedthrough it creates spike in transition clock in the previous stage and i have to choose big CH

how can i cancel these spike

what kind of model switch (complementary, bootstrapped,... ) are suitable for sample and hold circuit