mohamis288

Full Member level 3

Hello,

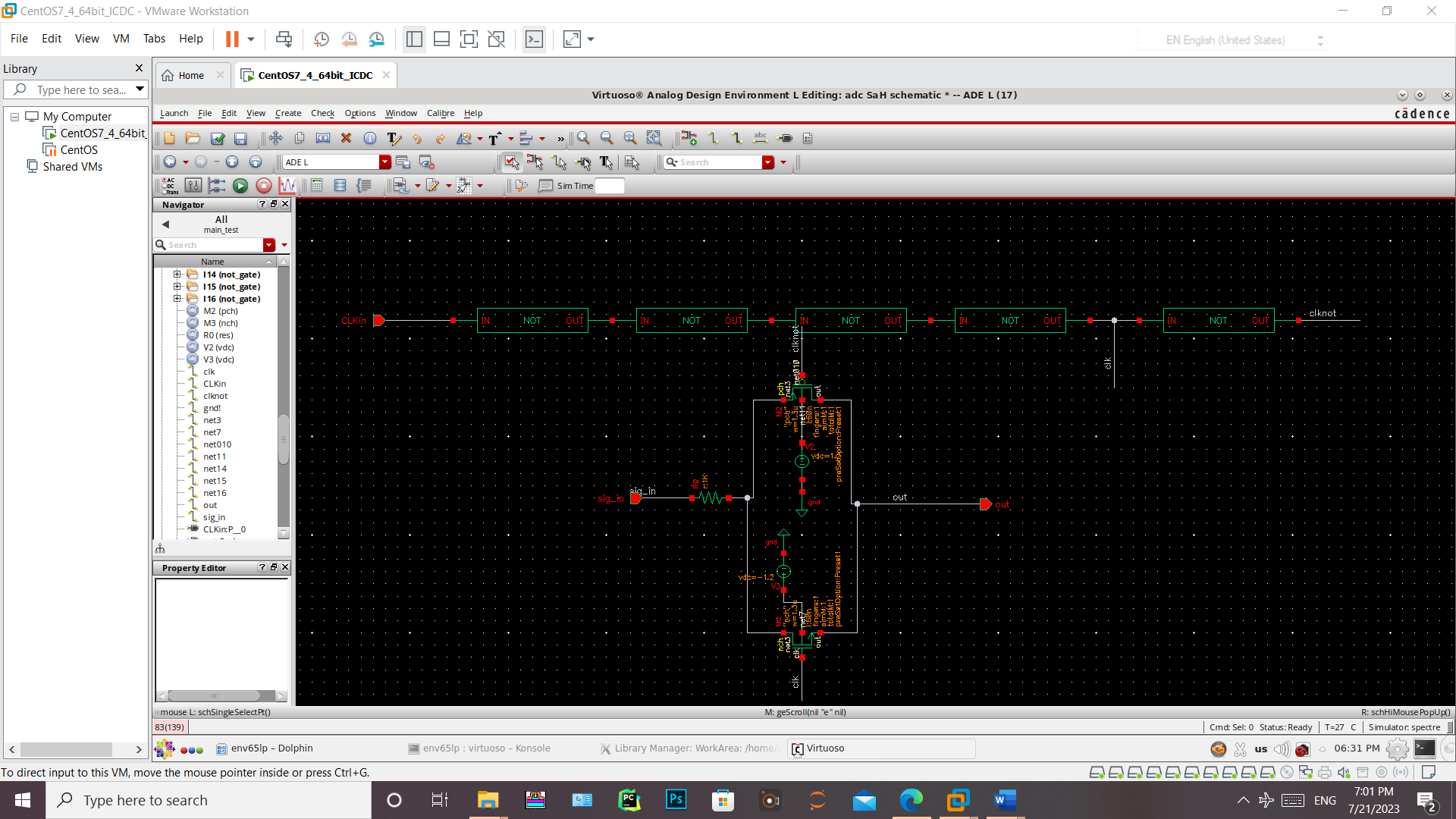

part of ADC is a Sample&Hold circuit. here is the circuit of my simple S&H circuit:

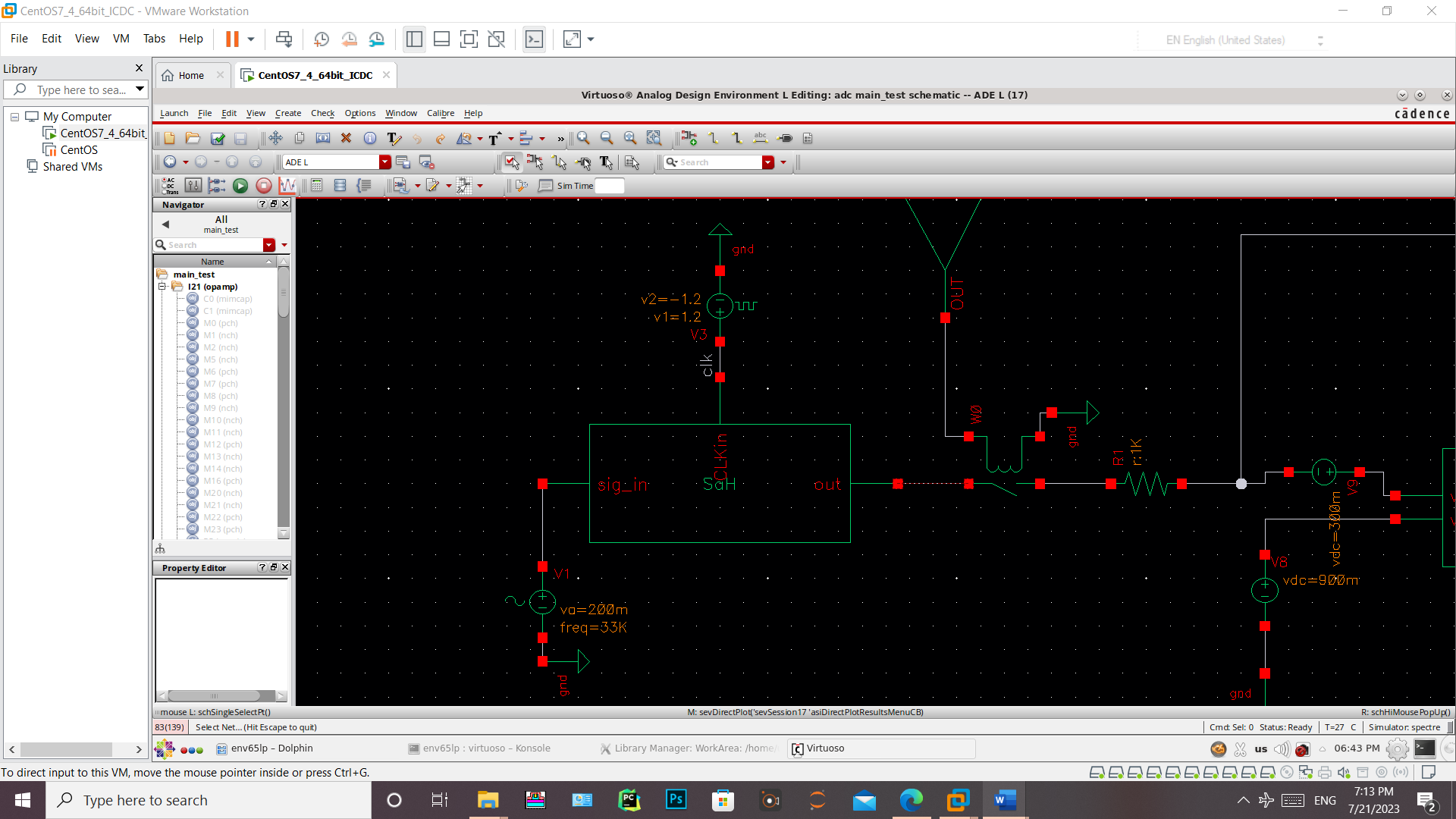

its symbol in the original circuit is shown in the following:

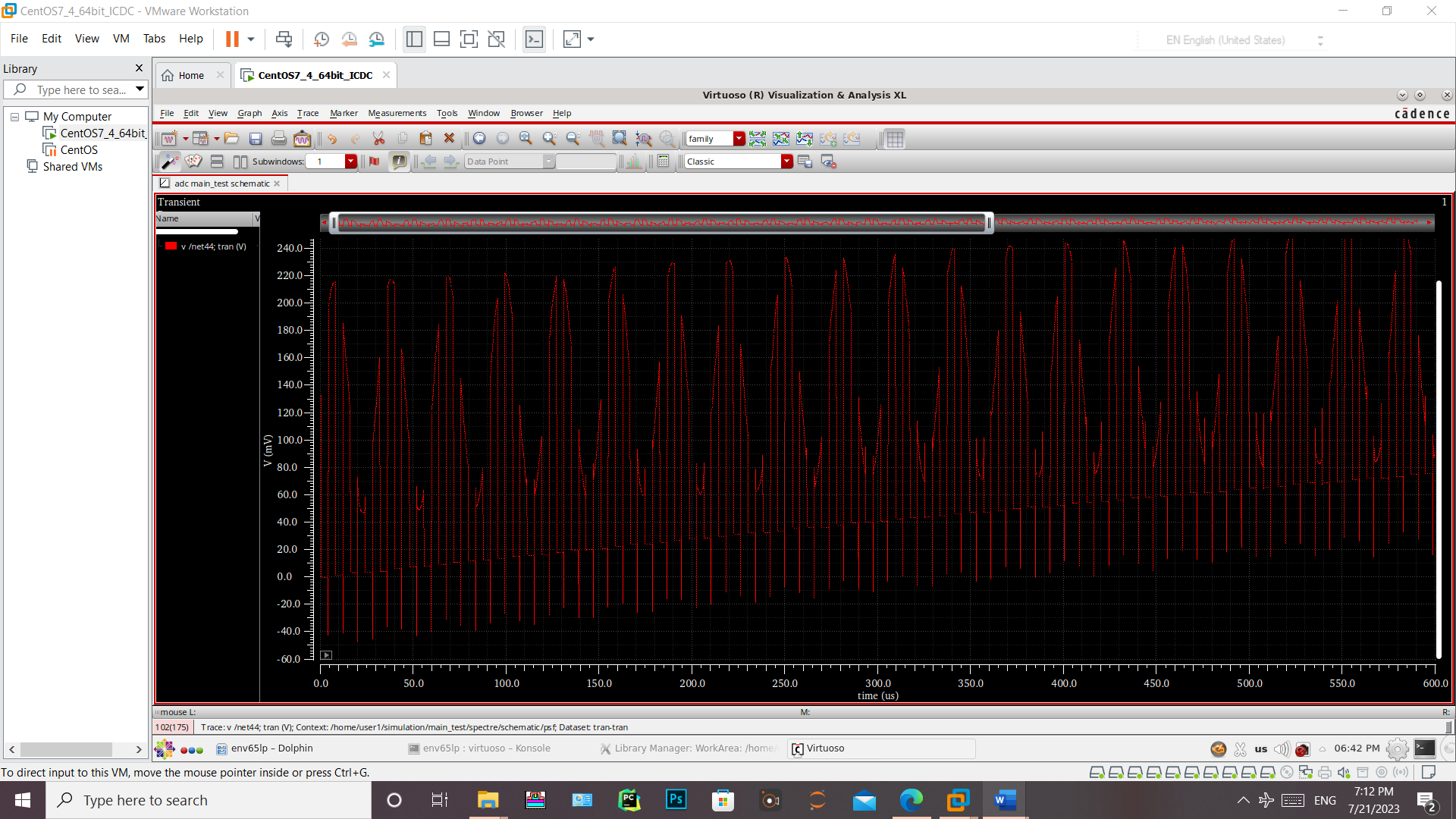

input signal is a 33KHz 200m volt sinusoidal wave with DC level of 300m V. sampling frequency is about 4 times of input frequency. it is used in a dual slope ADC. as shown below, output voltage of S&H circuit is in the transient state. it takes a lot of time to arrive at steady state, what can I do to overcome this problem?

part of ADC is a Sample&Hold circuit. here is the circuit of my simple S&H circuit:

its symbol in the original circuit is shown in the following:

input signal is a 33KHz 200m volt sinusoidal wave with DC level of 300m V. sampling frequency is about 4 times of input frequency. it is used in a dual slope ADC. as shown below, output voltage of S&H circuit is in the transient state. it takes a lot of time to arrive at steady state, what can I do to overcome this problem?