yefj

Advanced Member level 4

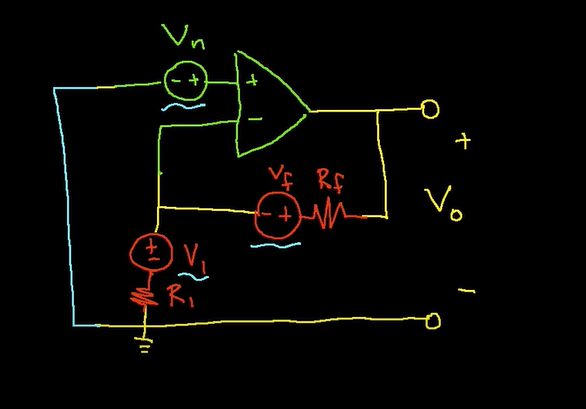

Hello, In this video we represent each component as a source of noise,but in real life the traces also play a role.

How can we simulate noise with the contribution of the traces connecting the components?

Thanks.

How can we simulate noise with the contribution of the traces connecting the components?

Thanks.