yefj

Advanced Member level 4

Hello, i have two issues when i build my circuit shown bellow:

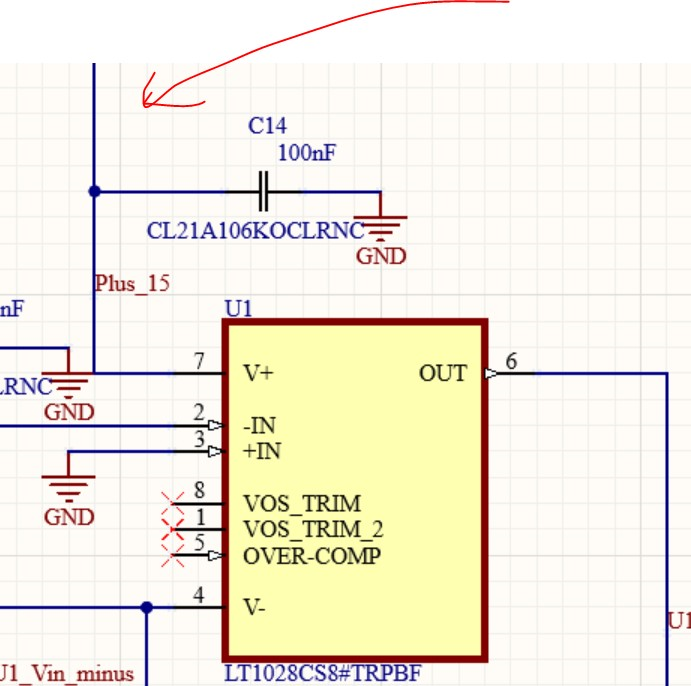

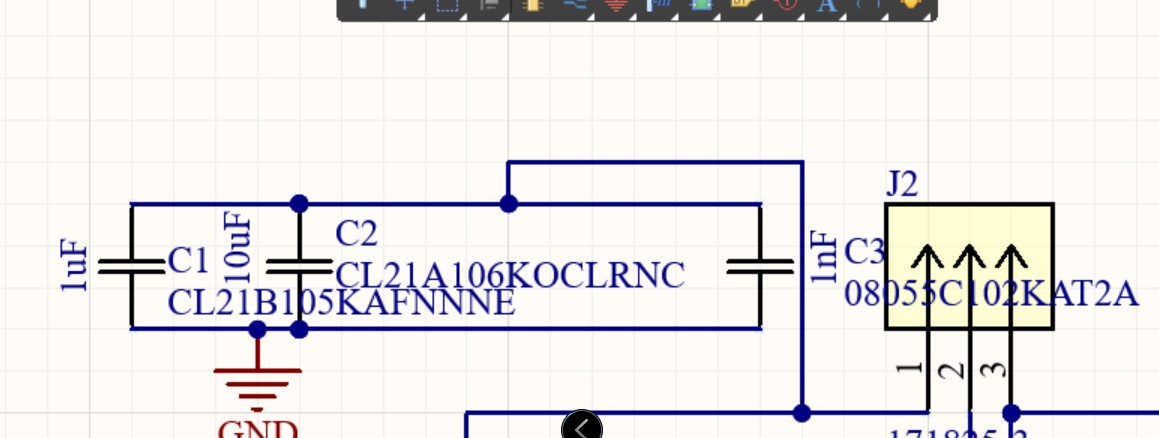

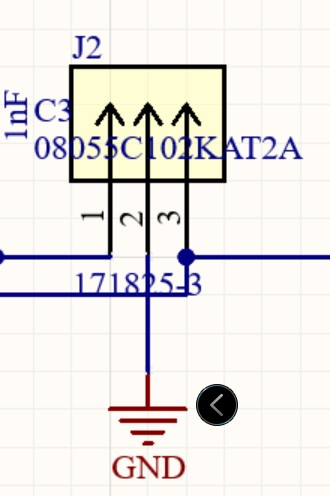

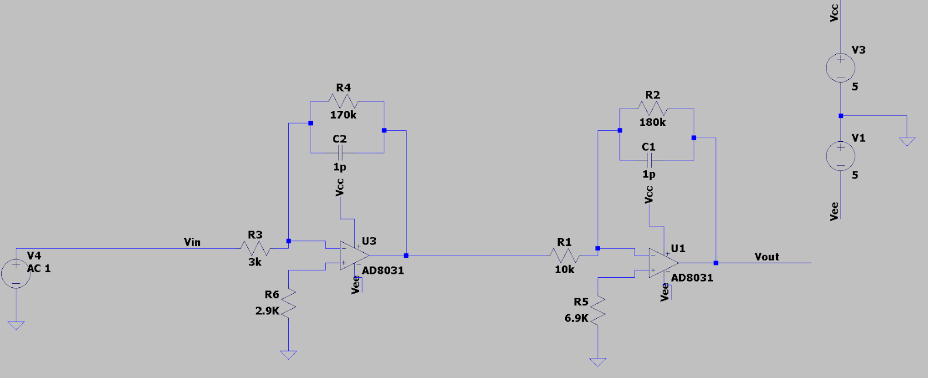

1.regarding dec i have added decouplin capacitor as shown bellow but i am not sure if its betther to connect them on the side to the ground plane or its better to connect them between traces connected pins 1-2 and 2-3 ?

2.regarding bypass capacitors i have connected 0.1uF near IC to ground plane with a VIA as shown below.

Is it ok ? maybe i need to connect them as power rail between traces going straing from pins?

How do i know that 0.1uF fits my needs for bypass?

Thanks.

1.regarding dec i have added decouplin capacitor as shown bellow but i am not sure if its betther to connect them on the side to the ground plane or its better to connect them between traces connected pins 1-2 and 2-3 ?

2.regarding bypass capacitors i have connected 0.1uF near IC to ground plane with a VIA as shown below.

Is it ok ? maybe i need to connect them as power rail between traces going straing from pins?

How do i know that 0.1uF fits my needs for bypass?

Thanks.