canlu

Newbie level 6

hi.

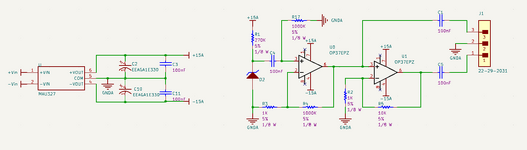

i have this circuit with op37 op-amp, and repeated three time.

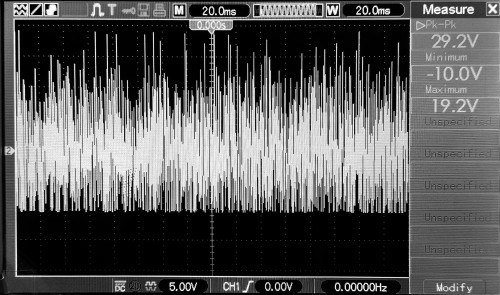

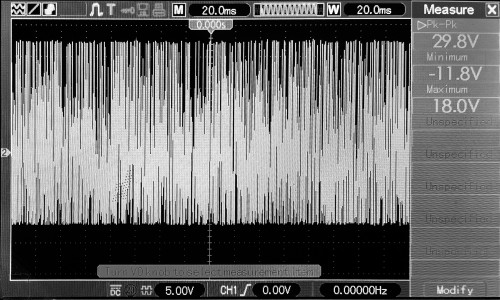

but at output i have different offset according to pictures:

every thig is same and resistor's are 1%.

even in the output i have mkt cap.

what can cause such behavier in this circuit?

i have this circuit with op37 op-amp, and repeated three time.

but at output i have different offset according to pictures:

every thig is same and resistor's are 1%.

even in the output i have mkt cap.

what can cause such behavier in this circuit?