melkord

Full Member level 3

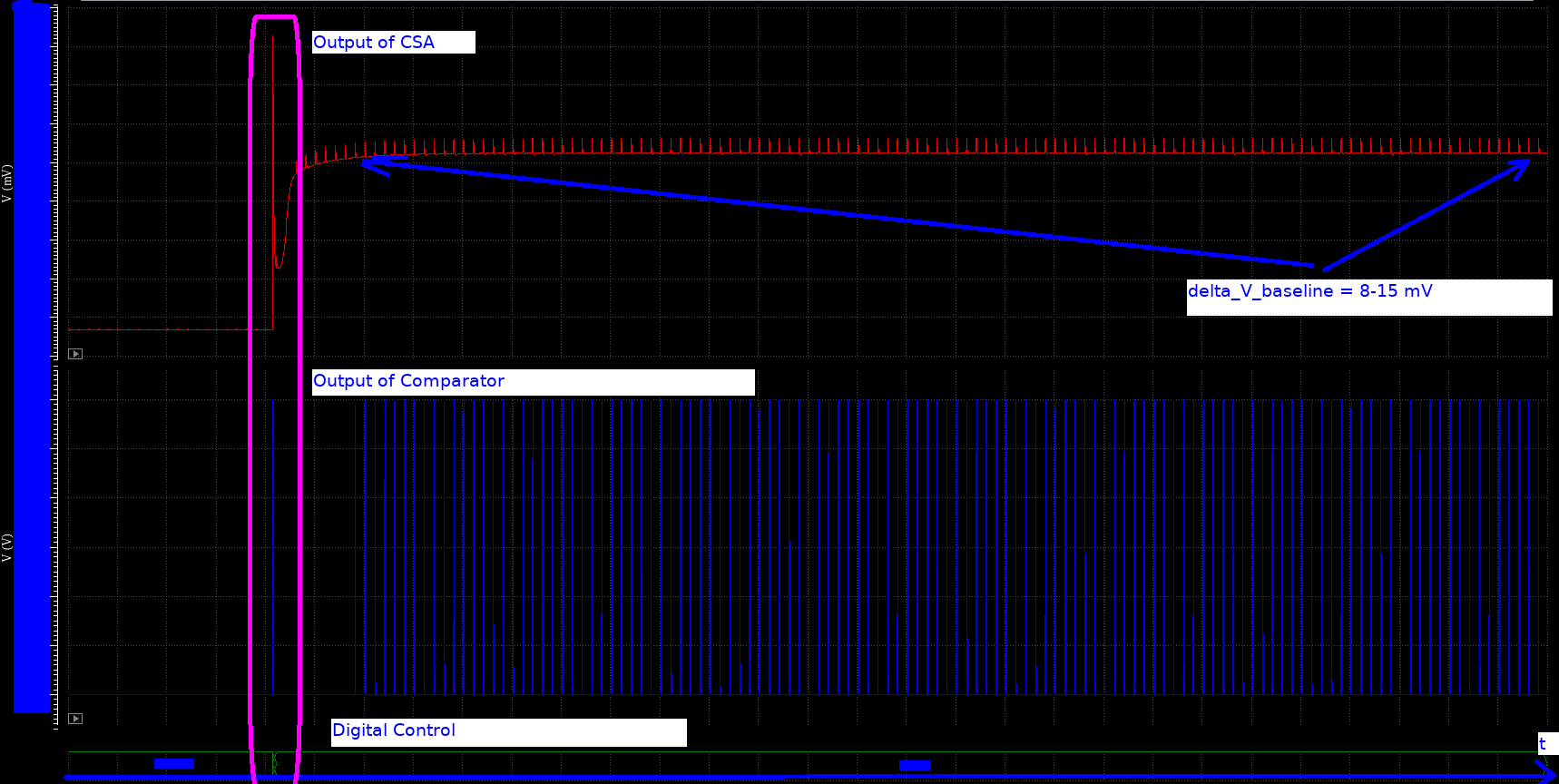

I have an array of, let's say, CSA-Comparator pair and a digital block to control this array.

As can be seen from the picture below, the changing of digital control signal affecting the analog signal, i.e., its baseline and amplitude.

This results to a pulse width variation on the comparator output.

The digital part has its own supply in this simulation.

How can I mitigate this?

As can be seen from the picture below, the changing of digital control signal affecting the analog signal, i.e., its baseline and amplitude.

This results to a pulse width variation on the comparator output.

The digital part has its own supply in this simulation.

How can I mitigate this?