fanshuo

Full Member level 5

- Joined

- Jun 21, 2007

- Messages

- 266

- Helped

- 8

- Reputation

- 16

- Reaction score

- 4

- Trophy points

- 1,298

- Location

- Netherlands

- Activity points

- 2,746

Why transistors working in sub-threshold region has the matching problem.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

tyanata said:It is not true, matching of transistors in weak inversion is not influenced by ΔVth.

So in weak inversion transistor have better matching.

malizevzek said:in sub-threshold region, all the device parameter deviations influence the mismatch through exponential term, as opposed to quadratic term in saturation.

tyanata said:So,

I have such a question.

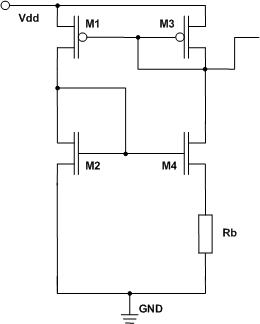

If we have simple bias circuit: two NMOS, two PMOS, and rezistor between source of one of the NMOS and ground.

What is better NMOS to be in weak invesrion or in strong?