yefj

Advanced Member level 4

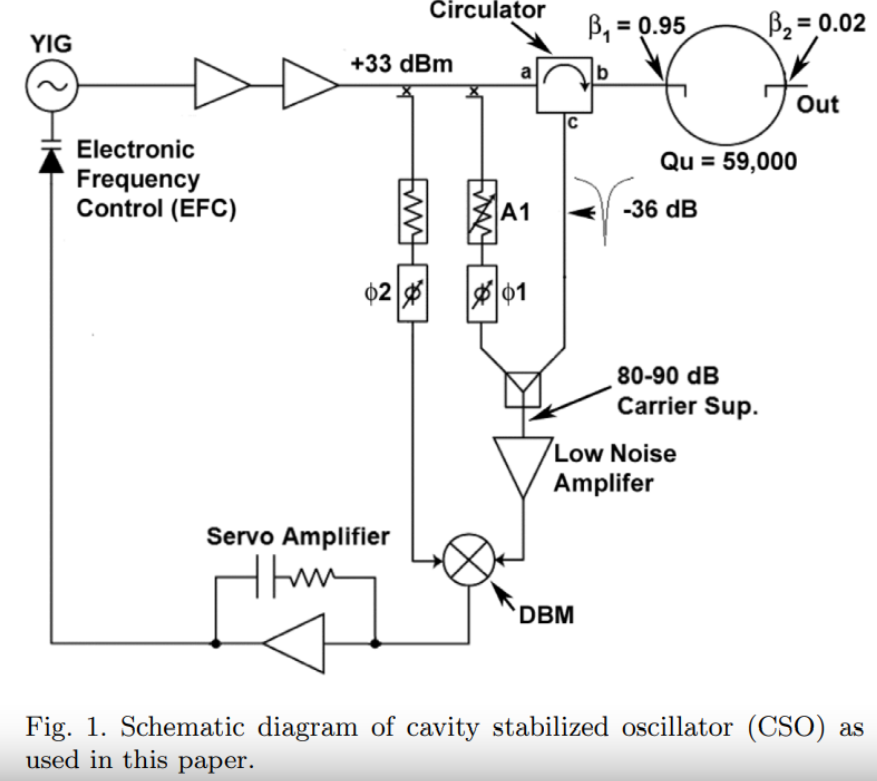

Hello,there is a circuit shown below taken from the attached article, where we put a YIG signal to a cavity resonator(from A to B) .

Then for feedback we lock on the point of the dip.

this dip is supposed to be a resonance of a cavity.

resonance is when the magnetic energy equals the electric energy maximal energ is stored in the cavity.

So why for feedback we lock on the cavity at this point?

Thanks.

Then for feedback we lock on the point of the dip.

this dip is supposed to be a resonance of a cavity.

resonance is when the magnetic energy equals the electric energy maximal energ is stored in the cavity.

So why for feedback we lock on the cavity at this point?

Thanks.