janlee

Newbie level 5

I wrote a state machine something like this:

--

process(clk,rst_n)

begin

if rst_n = '0' then

current_state <= s0;

elsif clk'event and clk = '1' then

current_state <= next_state;

-- toggle some bit according to state

...

end if;

end process;

process(clk)

begin

case current_state is

when s0 =>

if "some invent" then

next_state <= s1;

end if;

when s1 =>

if "some invent" then

next_state <= s2;

end if;

when s2 =>

if "some invent" then

next_state <= s3;

end if;

when others =>

next_state <= s0;

end case;

end process;

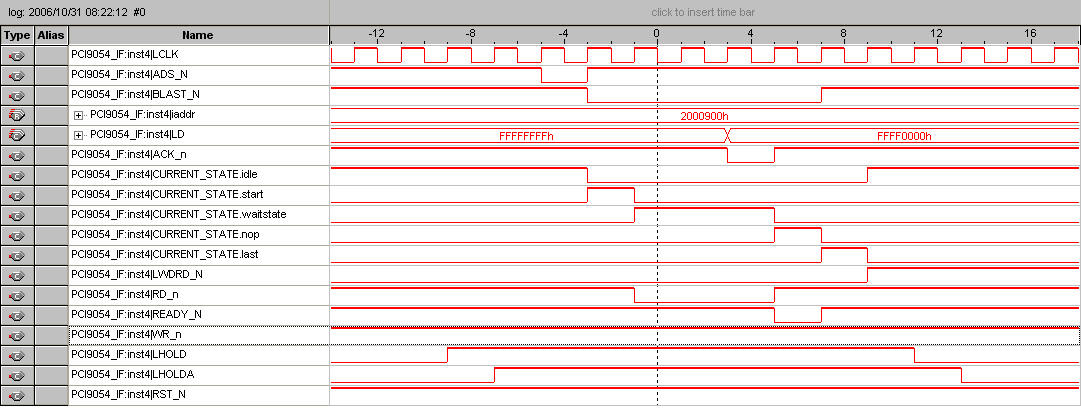

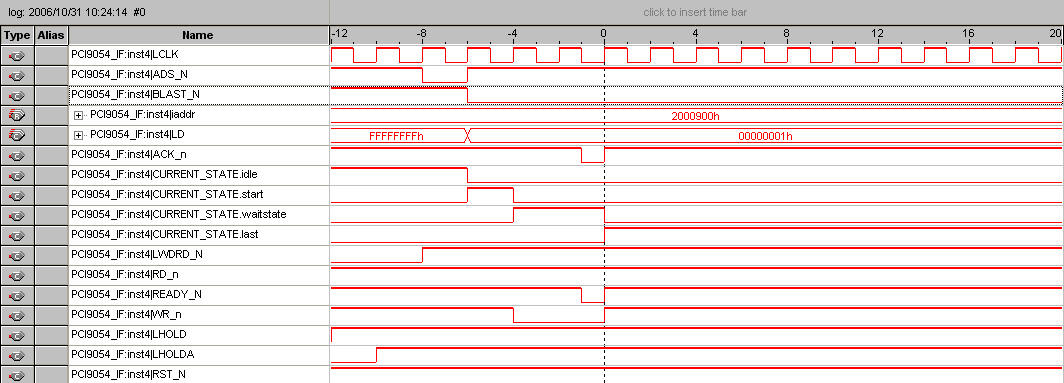

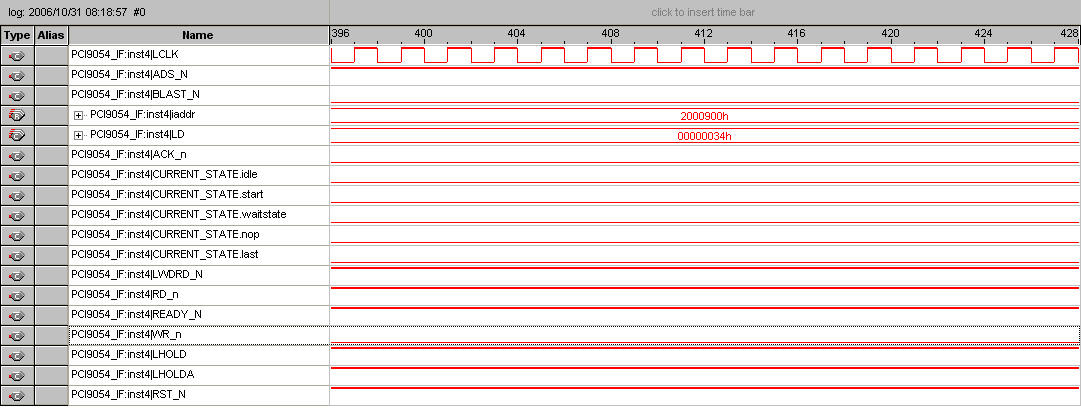

The problem is this state machine some times runs good , some times it runs into unknow state . I use altera signal tap II to trace all the state s0~s3.when state machine goes wrong ,s0~s3 are all '0',that is to say current state is not in the s0~s3. I was very puzzled now.

Is someone out there can give me some suggestions and coding style about state machine.

Many appreciations!

--

process(clk,rst_n)

begin

if rst_n = '0' then

current_state <= s0;

elsif clk'event and clk = '1' then

current_state <= next_state;

-- toggle some bit according to state

...

end if;

end process;

process(clk)

begin

case current_state is

when s0 =>

if "some invent" then

next_state <= s1;

end if;

when s1 =>

if "some invent" then

next_state <= s2;

end if;

when s2 =>

if "some invent" then

next_state <= s3;

end if;

when others =>

next_state <= s0;

end case;

end process;

The problem is this state machine some times runs good , some times it runs into unknow state . I use altera signal tap II to trace all the state s0~s3.when state machine goes wrong ,s0~s3 are all '0',that is to say current state is not in the s0~s3. I was very puzzled now.

Is someone out there can give me some suggestions and coding style about state machine.

Many appreciations!