Xenon02

Full Member level 3

Hello !

I want to a quick question about SPI.

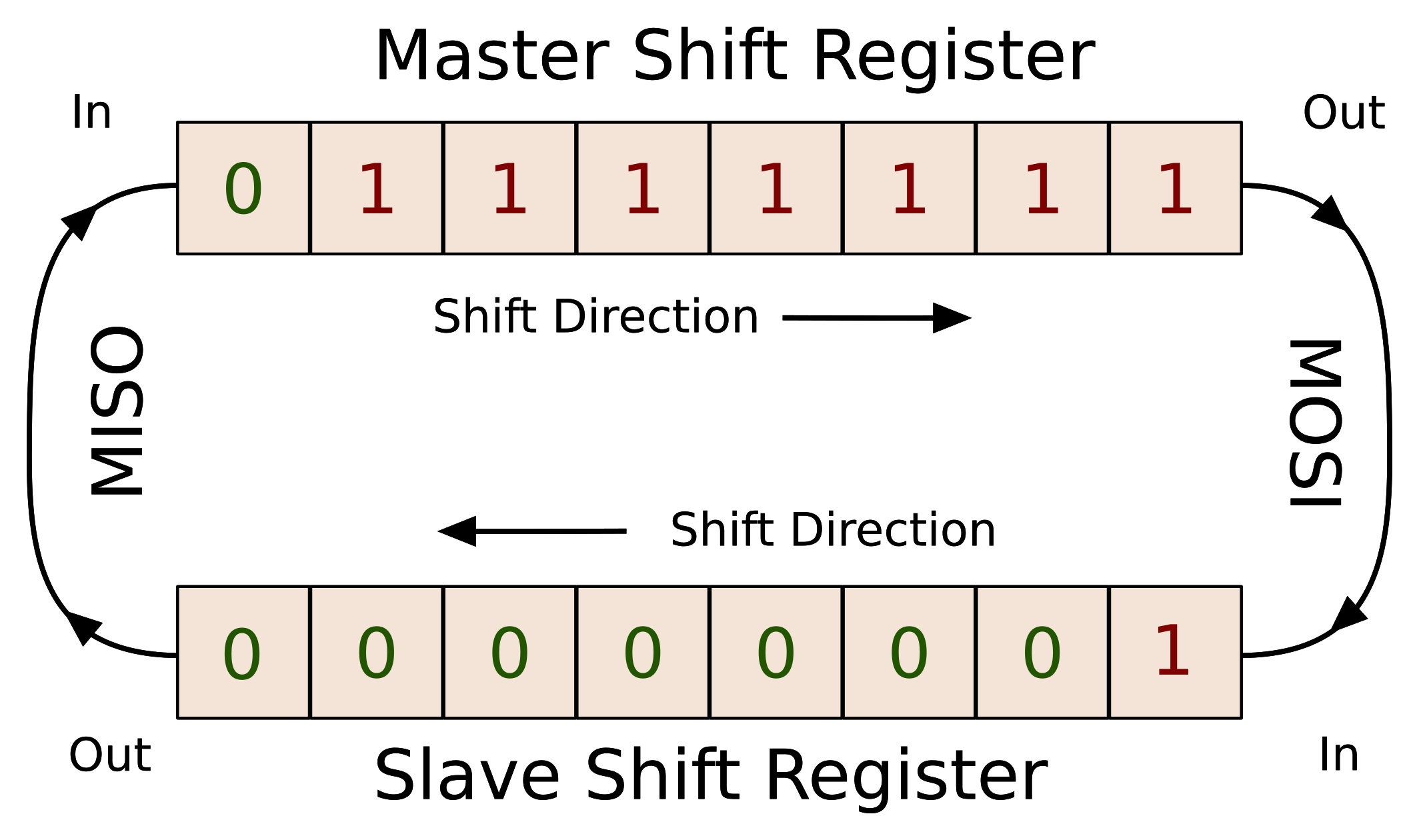

I've read alot about them and usually the SPI is shown with 8 bit registers like here :

And I've seen some videos and info that SPI usually have 16 bit registers and not 8 bit.

The thing is I am not sure what happens with one situation.

If I want to transmit 1 byte and receive 2 bytes then in total the whole transaction is 3 byte. So what happens with 4-th byte ? I know that 1st byte transmitted the master will receive dummy byte, and 2 bytes received by slave, the master will transmit 2 dummy bytes, but the 4th byte ? Is the 4th byte both dummy from master and dummy from slave ? Because the full transaction between Master and Slave for 16 bit register must be minimally 16 bits and not 8 bits like in the picture.

Second question is that whenever Master or Slave want's to transmit information the other side automatically fulls it's register with dummy byte ? For example Slave sends data to Master then Master fills his register with dummy byte and sends it ? Usually these dummy bytes are ignored but It's good to know if it's a hardware thing or what that fills the registers with something(like okey now slave you receive data so you must clear your register with "0"). Like what is connected more to shift registers ? What clears the registers and puts in dummy byte or data byte ? Dummy byte are usually "0" so there must be another register or something that puts into these register this "0" dummy byte. And I know that dummy byte doesn't have to be "0" or "1" it can be any random data.

It's hard to imagine this clear phase with simple picture (I've checked some more complex pictures but It was to complicated).

PS.

I came up with another thing : how it does that the Slave doesn't read the dummy bytes, how he ignores them (I know that R/W bite can be a solution but !), there was one example where I had to use Write bite to send dummy bytes so how does the device know that it is a dummy byte and not an overwrite data when it says (send dummy bytes 5-8) ? If I send 6 is it enough ? How does it know?

I want to a quick question about SPI.

I've read alot about them and usually the SPI is shown with 8 bit registers like here :

And I've seen some videos and info that SPI usually have 16 bit registers and not 8 bit.

The thing is I am not sure what happens with one situation.

If I want to transmit 1 byte and receive 2 bytes then in total the whole transaction is 3 byte. So what happens with 4-th byte ? I know that 1st byte transmitted the master will receive dummy byte, and 2 bytes received by slave, the master will transmit 2 dummy bytes, but the 4th byte ? Is the 4th byte both dummy from master and dummy from slave ? Because the full transaction between Master and Slave for 16 bit register must be minimally 16 bits and not 8 bits like in the picture.

Second question is that whenever Master or Slave want's to transmit information the other side automatically fulls it's register with dummy byte ? For example Slave sends data to Master then Master fills his register with dummy byte and sends it ? Usually these dummy bytes are ignored but It's good to know if it's a hardware thing or what that fills the registers with something(like okey now slave you receive data so you must clear your register with "0"). Like what is connected more to shift registers ? What clears the registers and puts in dummy byte or data byte ? Dummy byte are usually "0" so there must be another register or something that puts into these register this "0" dummy byte. And I know that dummy byte doesn't have to be "0" or "1" it can be any random data.

It's hard to imagine this clear phase with simple picture (I've checked some more complex pictures but It was to complicated).

PS.

I came up with another thing : how it does that the Slave doesn't read the dummy bytes, how he ignores them (I know that R/W bite can be a solution but !), there was one example where I had to use Write bite to send dummy bytes so how does the device know that it is a dummy byte and not an overwrite data when it says (send dummy bytes 5-8) ? If I send 6 is it enough ? How does it know?

Last edited: