syee10

Member level 3

Hi all,

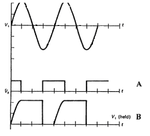

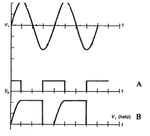

I am designing a simple sample and hold circuit where the input is a sinusoidal analog input and it is control by a TTL compatible square wave (waveform A). The result waveform i should get is waveform B in the attach file but i tried a millions time i still cant get the same waveform. Someone there can help me out? I had attached all the file in the attachment..

I am designing a simple sample and hold circuit where the input is a sinusoidal analog input and it is control by a TTL compatible square wave (waveform A). The result waveform i should get is waveform B in the attach file but i tried a millions time i still cant get the same waveform. Someone there can help me out? I had attached all the file in the attachment..