fpmkh0

Newbie level 6

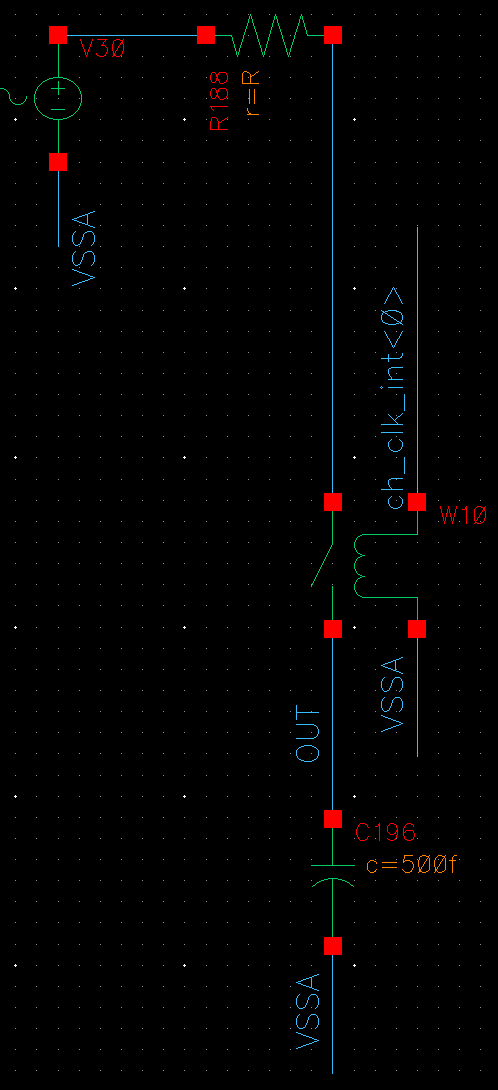

Hi, I have a simple sample and hold circuit. The resistor is 100 ohm, the switch is ideal (Ron=1u, Roff=1T), capacitor is 500fF. If there was no switch and I run a simple noise simulation in virtuoso, for PSD, I see exactly 4KTR in low frequencies with a LPF shape (due to the capacitor), and if I integrate from DC (100Hz) to 1THz, I see exactly KT/C. So everything is as expected.

Now I put the switch in circuit. I clock the switch with a 50% duty cycle clock and frequency is fs=1GHz. I will now have noise folding from every frequency above fs/2 (500MHz) back to the region of 0 to fs/2. I expected that if I integrate the noise from DC to fs/2, I'd see again KT/C. But that's not the case. Shouldn't it be the case? Also, I see that changing the duty cycle of the clock also changes the result (integrated noise from DC to fs/2). I thought it shouldn't be the case. Can someone experienced help me with this? Are my expectations wrong? If yes, what should I expect to see from Pnoise simulation compared to a simple noise (without switch). How can I see the noise folding effect?

For my simulation setup, I put maxacfreq in PSS to be 1THz. And in Pnoise to do over full spectrum.

Now I put the switch in circuit. I clock the switch with a 50% duty cycle clock and frequency is fs=1GHz. I will now have noise folding from every frequency above fs/2 (500MHz) back to the region of 0 to fs/2. I expected that if I integrate the noise from DC to fs/2, I'd see again KT/C. But that's not the case. Shouldn't it be the case? Also, I see that changing the duty cycle of the clock also changes the result (integrated noise from DC to fs/2). I thought it shouldn't be the case. Can someone experienced help me with this? Are my expectations wrong? If yes, what should I expect to see from Pnoise simulation compared to a simple noise (without switch). How can I see the noise folding effect?

For my simulation setup, I put maxacfreq in PSS to be 1THz. And in Pnoise to do over full spectrum.

Last edited: