mrinalmani

Advanced Member level 1

- Joined

- Oct 7, 2011

- Messages

- 467

- Helped

- 60

- Reputation

- 121

- Reaction score

- 59

- Trophy points

- 1,318

- Location

- Delhi, India

- Activity points

- 5,351

Thanks everyone for the reply.

It is unlikely that the readings are due to EMI at 200KHz. Readings due to EMI pick-up generally diminish by reducing the loop area of the oscilloscope probe terminals. I had varied the loop area of the probe a great deal but the readings didn't show even the slightest of change.

I suspected the ripple to be a glitches at 200KHz, but the waveform is too even and smooth and is more likely ripple than glitch.

The ripple is probably due to the ESL of the electrolytic capacitors.

The inductance due to the loop formed by 2cm long leads, placed 1.5cm apart is roughly 45nH.

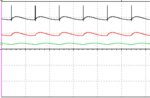

Here is the simulation result after putting a 45nH in series with the electrolytic capacitors and 1nH in series with ceramic capacitors.

RED: Ceramic cap voltage (V2)

GREEN: Electrolytic cap voltage (V1)

BLACK: Rail voltage (V3)

- - - Updated - - -

The electrolytic caps are hardly absorbing any current, their voltage is almost constant and not much effected by the ripple in the rail.

It is unlikely that the readings are due to EMI at 200KHz. Readings due to EMI pick-up generally diminish by reducing the loop area of the oscilloscope probe terminals. I had varied the loop area of the probe a great deal but the readings didn't show even the slightest of change.

I suspected the ripple to be a glitches at 200KHz, but the waveform is too even and smooth and is more likely ripple than glitch.

The ripple is probably due to the ESL of the electrolytic capacitors.

The inductance due to the loop formed by 2cm long leads, placed 1.5cm apart is roughly 45nH.

Here is the simulation result after putting a 45nH in series with the electrolytic capacitors and 1nH in series with ceramic capacitors.

RED: Ceramic cap voltage (V2)

GREEN: Electrolytic cap voltage (V1)

BLACK: Rail voltage (V3)

- - - Updated - - -

The electrolytic caps are hardly absorbing any current, their voltage is almost constant and not much effected by the ripple in the rail.