Hamed94

Junior Member level 1

Hi,

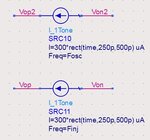

I have designed a mm-wave injection-locked frequency multiplier (or sub-harmonic injection-locked oscillator). My problem is that I don't know how to simulate its output phase noise. When I use simple HB simulation in ADS (Advanced Design System) or PSS simulation in Cadence, I get wrong results. I know that the output phase noise must be 20*logN dB higher than input's one where N is multiplication factor. Using Envelope simulation in ADS, I see that output is locked to the input's Nth harmonic.

Could you please help me to simulate output phase noise either in ADS or Cadence?

Any references or tutorials would be appreciated too.

Sincerely

HF

I have designed a mm-wave injection-locked frequency multiplier (or sub-harmonic injection-locked oscillator). My problem is that I don't know how to simulate its output phase noise. When I use simple HB simulation in ADS (Advanced Design System) or PSS simulation in Cadence, I get wrong results. I know that the output phase noise must be 20*logN dB higher than input's one where N is multiplication factor. Using Envelope simulation in ADS, I see that output is locked to the input's Nth harmonic.

Could you please help me to simulate output phase noise either in ADS or Cadence?

Any references or tutorials would be appreciated too.

Sincerely

HF