promach

Advanced Member level 4

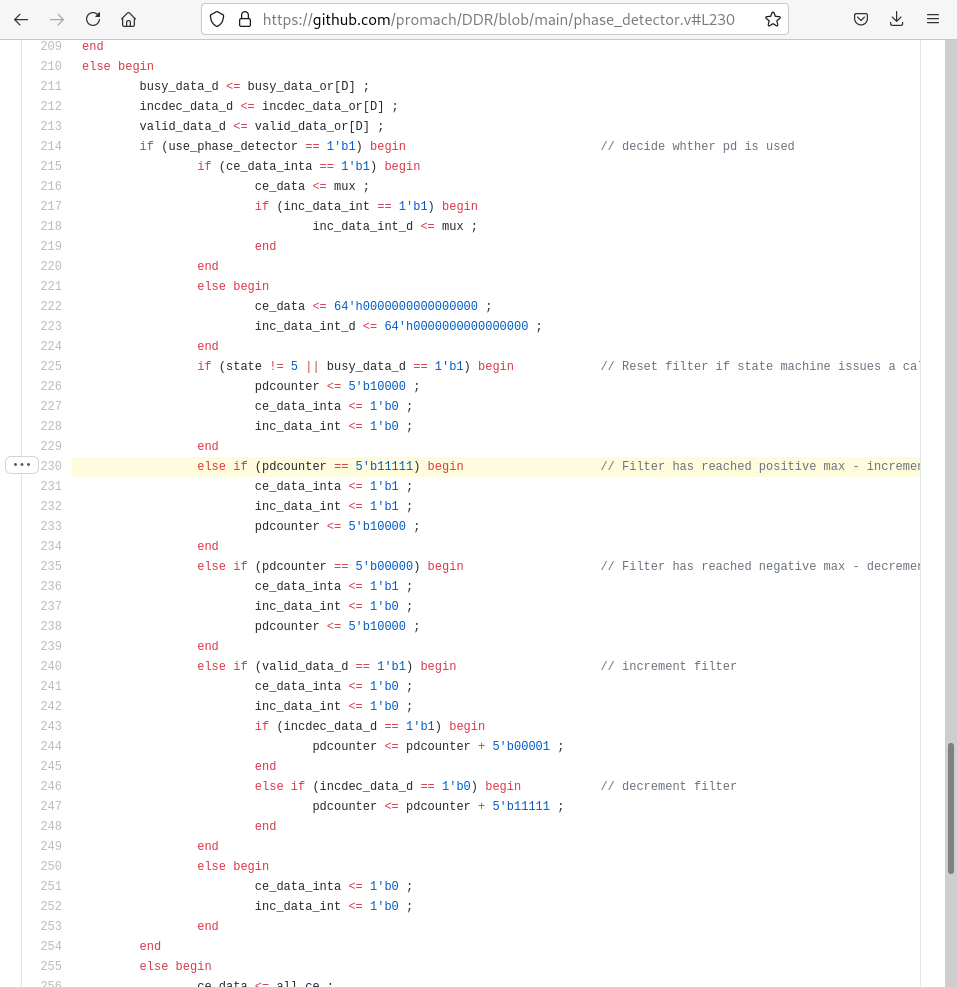

1) Do anyone know how this https://github.com/promach/DDR/blob/main/phase_detector.v works internally ?

2) What does it mean by MAX in Figure 9 of XAPP1064 appnote ?

3) Could anyone explain what it means by Early Data Sampling and Late Data Sampling ?

4) As for why is it 5 bits wide for pdcounter , someone told me that the verilog code only supports 32 (which is equivalent to 25) steps, but that is 1/8 of the total possible delay steps (256 delay taps) ?

2) What does it mean by MAX in Figure 9 of XAPP1064 appnote ?

3) Could anyone explain what it means by Early Data Sampling and Late Data Sampling ?

4) As for why is it 5 bits wide for pdcounter , someone told me that the verilog code only supports 32 (which is equivalent to 25) steps, but that is 1/8 of the total possible delay steps (256 delay taps) ?