olrac_s

Newbie level 3

Hello to everybody!

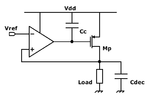

I've a situation like this one:

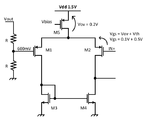

Due to the limited input swing range I cannot apply a signal biased at 1.2V if the power supply Vdd is at 1.5V. So I'm obliged to use a voltage divider at one input of the differential stage.

For my application ( a low noise LDO ) i cannot use that resistors because they are too noisy. But at the same time I would like to maintain the same topology (n MOS mirror) for noise and PSRR performances.

How can I extend input swing? or shift the level of the input introducing less noise?

Thanks so much to everybody!

I've a situation like this one:

Due to the limited input swing range I cannot apply a signal biased at 1.2V if the power supply Vdd is at 1.5V. So I'm obliged to use a voltage divider at one input of the differential stage.

For my application ( a low noise LDO ) i cannot use that resistors because they are too noisy. But at the same time I would like to maintain the same topology (n MOS mirror) for noise and PSRR performances.

How can I extend input swing? or shift the level of the input introducing less noise?

Thanks so much to everybody!