TXRX

Full Member level 2

Hi,

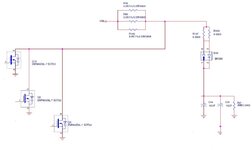

I Attached schema with 3 MOSFETs that prevent from capacitors C34, C35 to charge at 3 different time interval.

Do you think that MOSFETs can be damaged from from differnet timing of satuartion for each MOSFET ?

I put a Diodes that protect from situation that the capacitors charge for voltage and the MOSFET will discharge the capacitors and will develop a peak of current at MOSFET.

Thanks,

Doron

I Attached schema with 3 MOSFETs that prevent from capacitors C34, C35 to charge at 3 different time interval.

Do you think that MOSFETs can be damaged from from differnet timing of satuartion for each MOSFET ?

I put a Diodes that protect from situation that the capacitors charge for voltage and the MOSFET will discharge the capacitors and will develop a peak of current at MOSFET.

Thanks,

Doron