Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

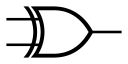

Moore is combinational,

primitive example

Let C= {Not A & Not B} OR {A & B}

we say here C = Exclusive NOR of {A,B}

Code VHDL - [expand]