Junus2012

Advanced Member level 5

Dear friends,

I am presenting an issue of layout matching between the core amplifier circuit to the biasing circuit,

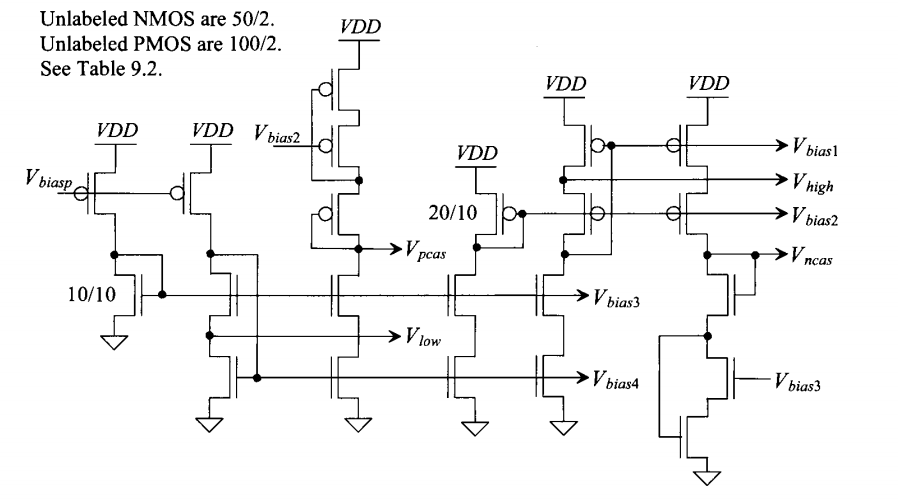

The biasing circuit is designed in separate cell, as the one shown below

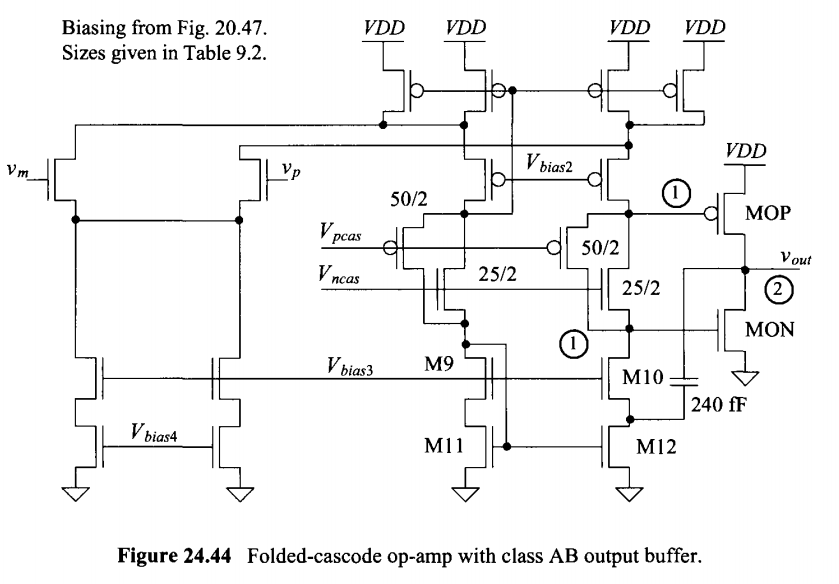

The core amplifier shown below is also designed in different cell, as the one shown below

My concern is that, how we would be assure that vbias voltages (vbias1, vbias2, vbias3, vbias4, vncas, vpcas) from the biasing circuit will be matched to the amplifier.

In the same time, thinking to build the biasing circuit in the same amplifier cell and matching them during layout is not easy solution for two reasons because design with hierarchy is more preferable and because the biasing circuit is biasing other different circuit. Therefore if we embeds the biasing circuit with the amplifier core will require to design and biasing circuit for every sub block in electronic system design.

Thank you very much

Best Regards

I am presenting an issue of layout matching between the core amplifier circuit to the biasing circuit,

The biasing circuit is designed in separate cell, as the one shown below

The core amplifier shown below is also designed in different cell, as the one shown below

My concern is that, how we would be assure that vbias voltages (vbias1, vbias2, vbias3, vbias4, vncas, vpcas) from the biasing circuit will be matched to the amplifier.

In the same time, thinking to build the biasing circuit in the same amplifier cell and matching them during layout is not easy solution for two reasons because design with hierarchy is more preferable and because the biasing circuit is biasing other different circuit. Therefore if we embeds the biasing circuit with the amplifier core will require to design and biasing circuit for every sub block in electronic system design.

Thank you very much

Best Regards