preethi19

Full Member level 5

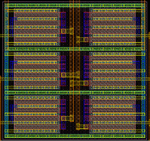

Hi i need to match 5 transistor (A,B,C,D,E) each having 2 fingers. So the total is 10. So 3x4=12.. So i add 2 dummies (0) and i have laid them as

D E 0

A B C

-------

A B C

D E 0

Is this a right way to do. Or should i make an even square matrix by adding 4x4=16... So by adding 6 dummies. Am i missing something??? Any tip while generally doing layout. Thanks!!!!

D E 0

A B C

-------

A B C

D E 0

Is this a right way to do. Or should i make an even square matrix by adding 4x4=16... So by adding 6 dummies. Am i missing something??? Any tip while generally doing layout. Thanks!!!!