KronosX

Newbie

Hello,

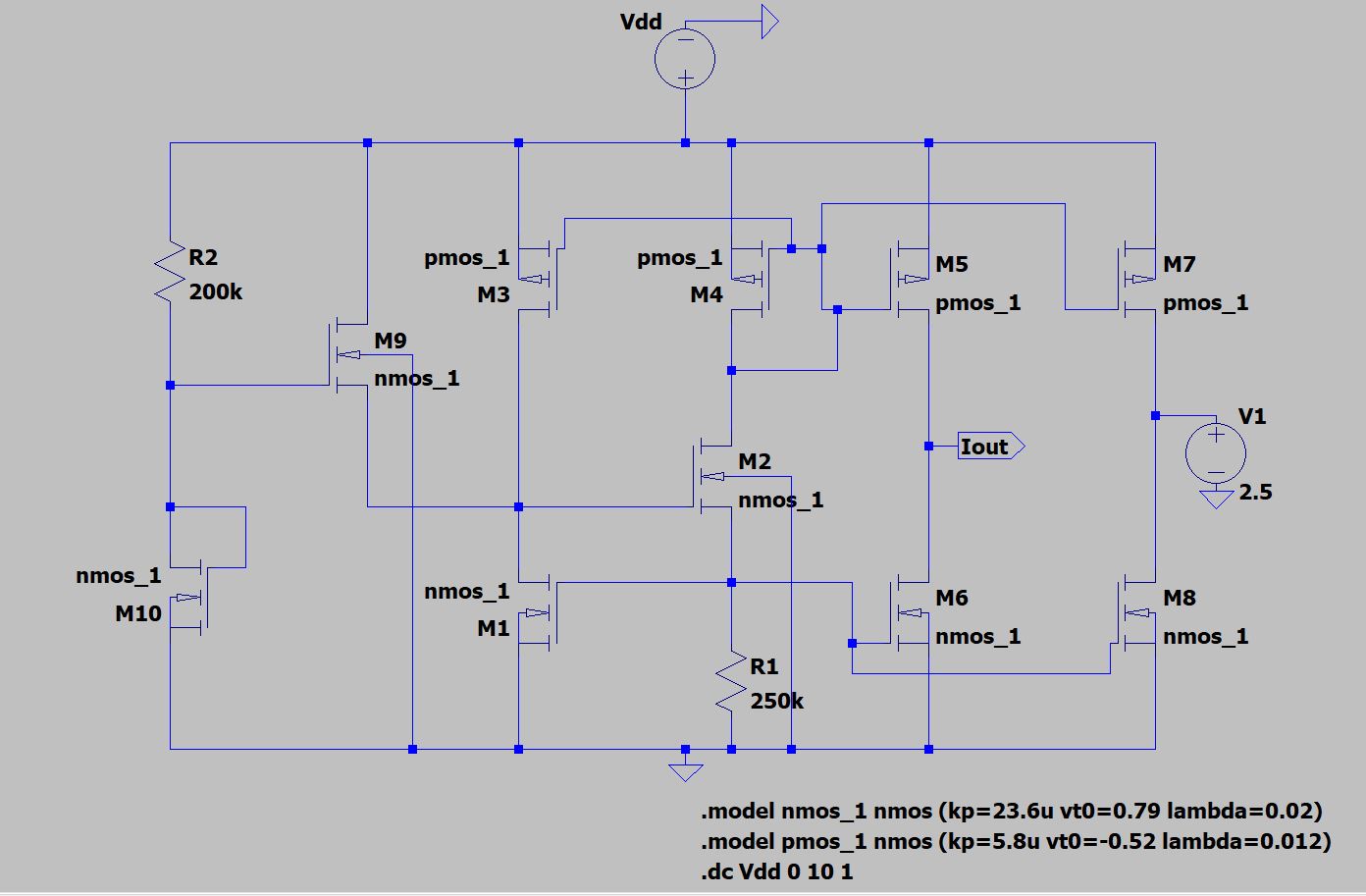

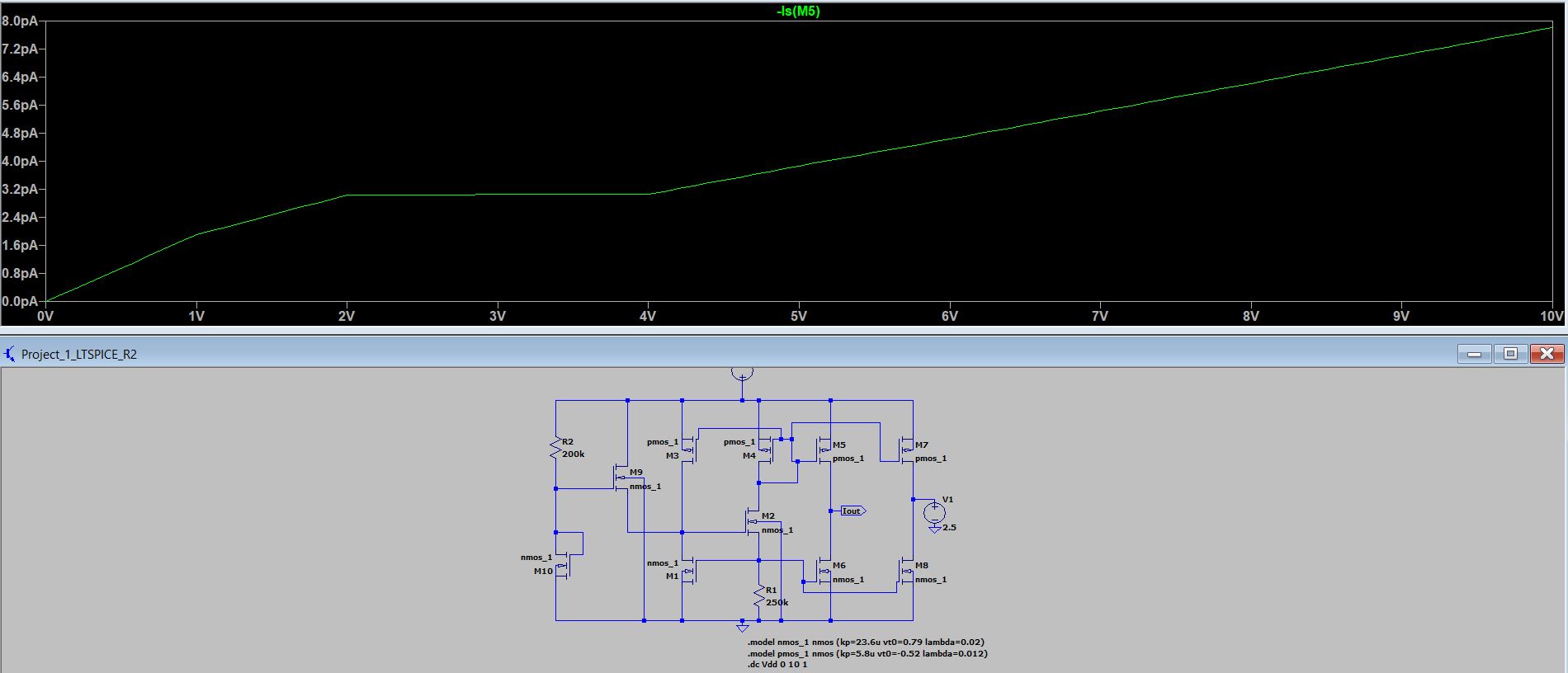

I need help in plotting the output current vs the drain voltage from 0 to 10 Volts.

I'm not sure what am I doing wrong with my simulation.

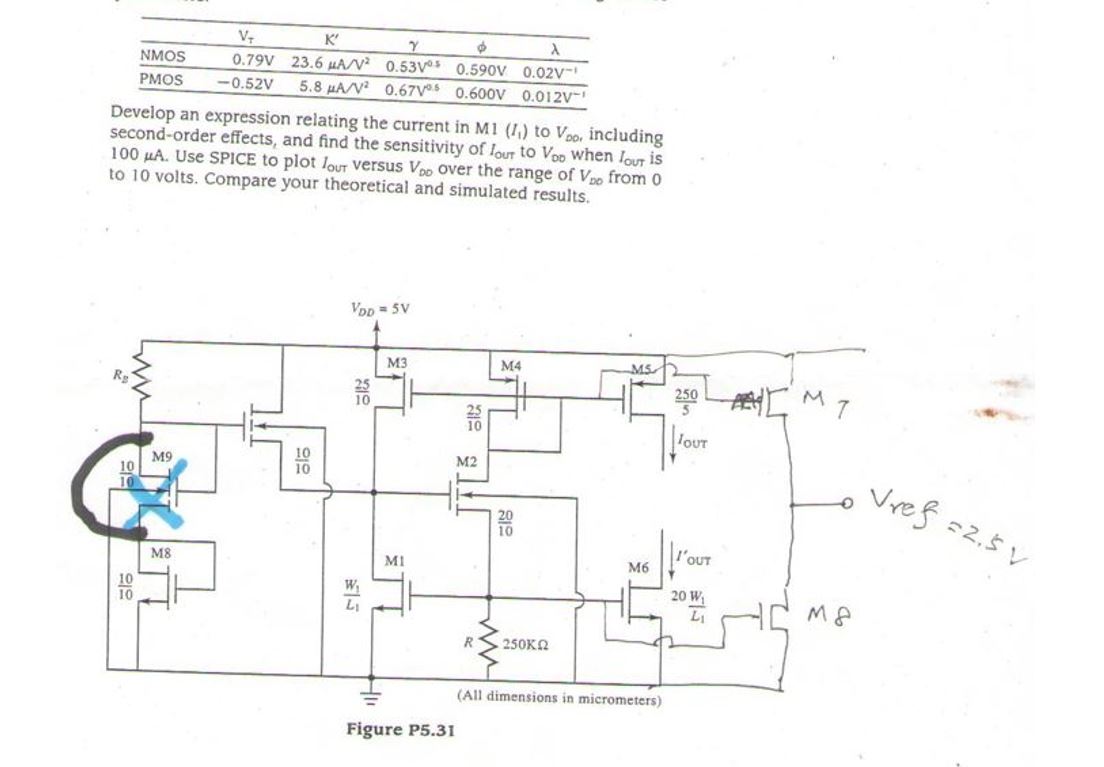

I added the width and length of all transistors and set the model to match the parameters specified.

I need help in plotting the output current vs the drain voltage from 0 to 10 Volts.

I'm not sure what am I doing wrong with my simulation.

I added the width and length of all transistors and set the model to match the parameters specified.