STHOTA

Junior Member level 1

Hello,

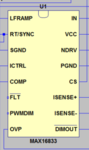

I'm working on IC MAX 16833 chip as an LED driver in LTspice simulation.

I was facing an error saying "Shorted voltage source: u1:vg2"

u1 is the pin name and there are no other pins like vg2 on the chip or anywhere on the board.

But the circuit was a weel established one already and all my connections were perfect.

If anyone could help me solve that error, I can run it.

Thanks for your help!!

I'm working on IC MAX 16833 chip as an LED driver in LTspice simulation.

I was facing an error saying "Shorted voltage source: u1:vg2"

u1 is the pin name and there are no other pins like vg2 on the chip or anywhere on the board.

But the circuit was a weel established one already and all my connections were perfect.

If anyone could help me solve that error, I can run it.

Thanks for your help!!