celebrevida

Member level 2

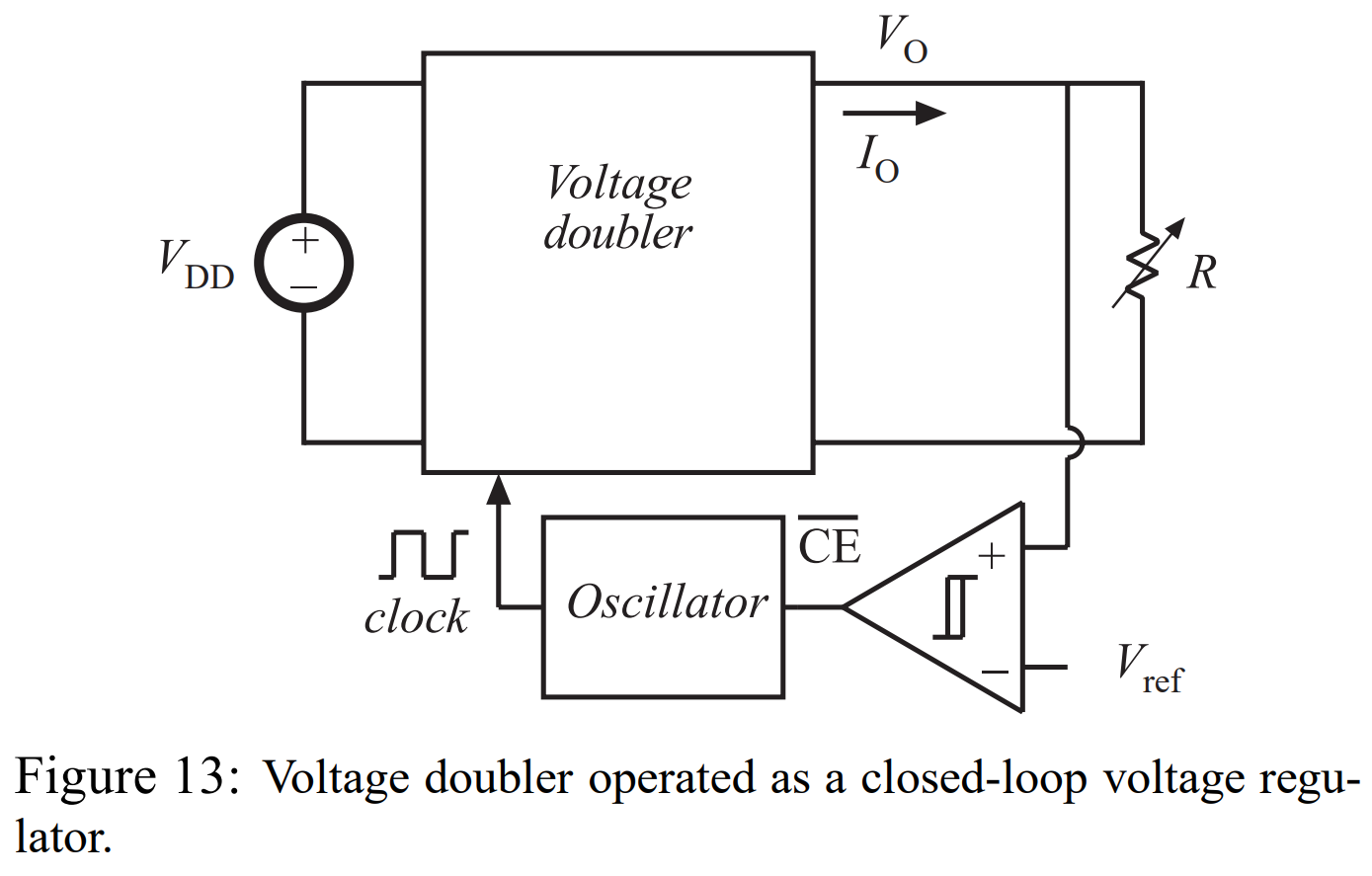

I am designing the following circuit:

The voltage doubler is just the standard crossed couple voltage doubler.

The oscillator is just a ring oscillator with a NAND-gate to provide enable functionality.

I used a behavioral model for the schmitt trigger comparator.

I am able to get it to work in LTSpice and it seems to work fine.

However, how do I perform loopgain analysis to determine stability (phase margin) of this closed-loop system?

Unlike, say, an LDO regulator where you can break the loop and perform AC/LSTB analysis directly, I don't think you can do that with the bang-bang type feedback control.

So how do I approach this?

Thanks for any help!

The voltage doubler is just the standard crossed couple voltage doubler.

The oscillator is just a ring oscillator with a NAND-gate to provide enable functionality.

I used a behavioral model for the schmitt trigger comparator.

I am able to get it to work in LTSpice and it seems to work fine.

However, how do I perform loopgain analysis to determine stability (phase margin) of this closed-loop system?

Unlike, say, an LDO regulator where you can break the loop and perform AC/LSTB analysis directly, I don't think you can do that with the bang-bang type feedback control.

So how do I approach this?

Thanks for any help!