promach

Advanced Member level 4

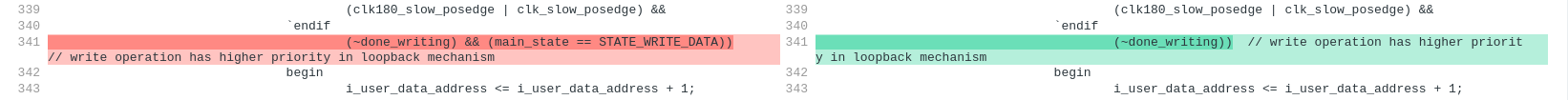

I have singled out the code modification that leads to routing error.

I removed the main_state signal because as a signal within the high-speed clock (ck) domain, it is not supposed to be interfering with low-speed clock (clk) domain stuff, and would only work with Micron simulation where it only uses a single clock domain (since there is no serdes in micron simulation).

However, it is this code modification on removal of "main_state" variable that leads to routing error, because upon variable removal, this IODELAY primitive is now no longer unconnected and have to be placed and routed.

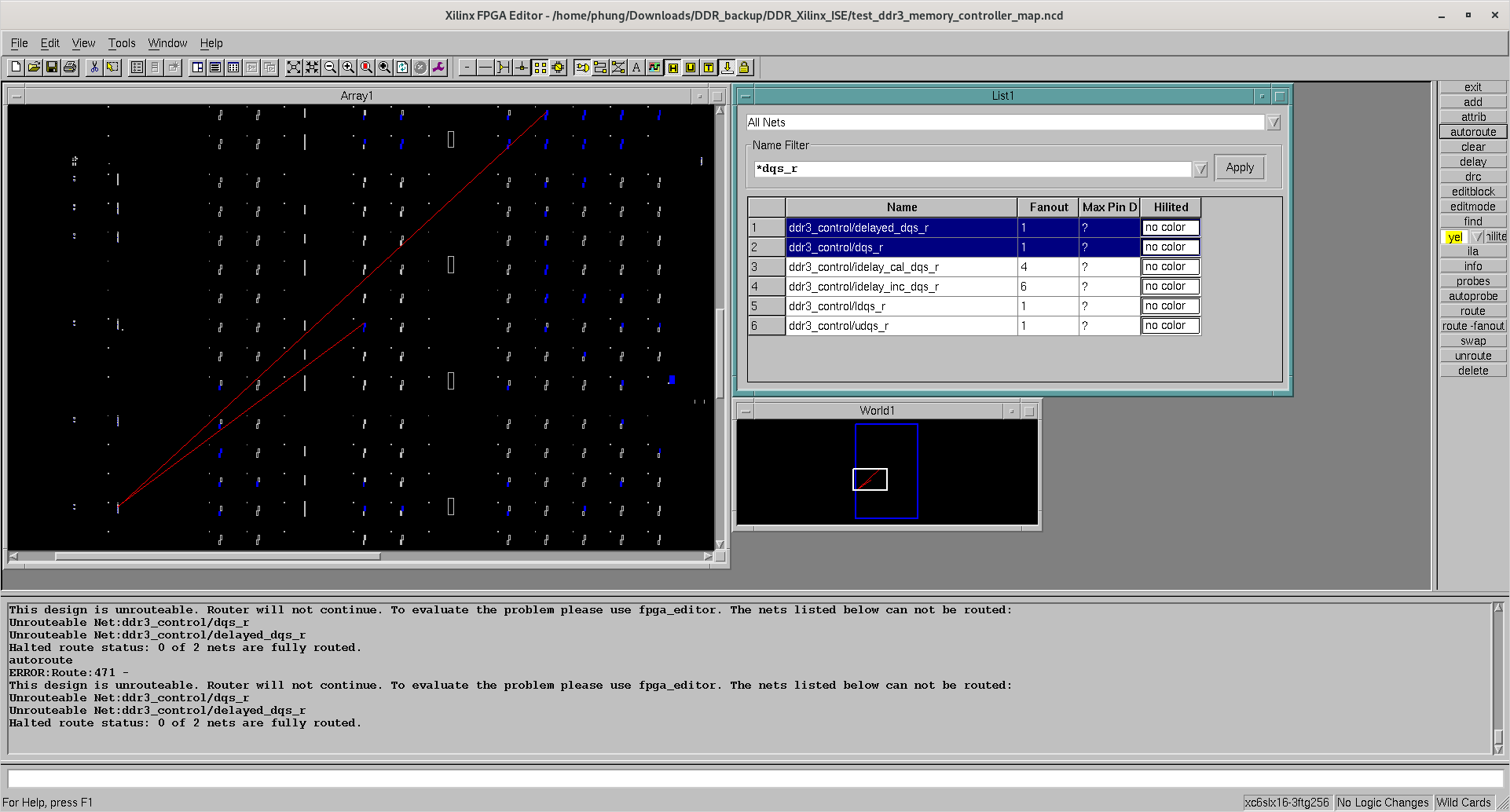

how to use FPGA editor to investigate this routing issue ?

Note: I had also attached a zip file containing the whole ISE project inside this thread.

I removed the main_state signal because as a signal within the high-speed clock (ck) domain, it is not supposed to be interfering with low-speed clock (clk) domain stuff, and would only work with Micron simulation where it only uses a single clock domain (since there is no serdes in micron simulation).

However, it is this code modification on removal of "main_state" variable that leads to routing error, because upon variable removal, this IODELAY primitive is now no longer unconnected and have to be placed and routed.

Code:

Starting Router

ERROR:Route:471 - This design is unrouteable.

Router will not continue.

To evaluate the problem please use fpga_editor.

The nets listed below can not be routed:

Unrouteable Net:ddr3_control/dqs_r

Unrouteable Net:ddr3_control/delayed_dqs_r

Total REAL time to Router completion: 2 secs

Total CPU time to Router completion: 2 secshow to use FPGA editor to investigate this routing issue ?

Note: I had also attached a zip file containing the whole ISE project inside this thread.

Attachments

Last edited: