Mabrok

Full Member level 4

Hi,

I have design power amplifier using ADS. During the simulation the S11 was good, but after fabricated the design the response was shifted from the original frequency which is 3.5 GHz to 2.5 GHz. what cause this big shifting?

the input matching was aimed to match complex impedance 5+j*1 to 50 ohm. The used matching technique was single quarter wave transformer.

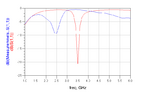

Herewith, i have attached the schematic of my design, measurements & simulation response (red simulation & blue measurements). Thanks in advanced

I have design power amplifier using ADS. During the simulation the S11 was good, but after fabricated the design the response was shifted from the original frequency which is 3.5 GHz to 2.5 GHz. what cause this big shifting?

the input matching was aimed to match complex impedance 5+j*1 to 50 ohm. The used matching technique was single quarter wave transformer.

Herewith, i have attached the schematic of my design, measurements & simulation response (red simulation & blue measurements). Thanks in advanced