bremenpl

Member level 3

Hello there,

I am designing a simple debounce mechanism in VHDL. I have the following problem. An internal counter (a variable) should be initially set to 0 or some value (ie. 100), depending on either the input is high or low at power up. I have no idea how to implement this. Is it even possible? At the moment my internal "key" state is initialized with input value, but for some reason this doesnt work. The first transition always fails (no debounce). I am using additional boolean generic's in order to enable the debounce for either up or low transitions.

.

.

.

In the top vhd file:

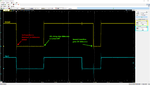

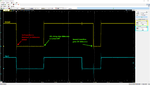

On the scope one can see that 1st transition is not correct, since falling edge should have debounce added (hystdown_dis => false). There should never be debounce added on rising edges and that is OK (hystup_dis => true).

I would appreciate all help.

I am designing a simple debounce mechanism in VHDL. I have the following problem. An internal counter (a variable) should be initially set to 0 or some value (ie. 100), depending on either the input is high or low at power up. I have no idea how to implement this. Is it even possible? At the moment my internal "key" state is initialized with input value, but for some reason this doesnt work. The first transition always fails (no debounce). I am using additional boolean generic's in order to enable the debounce for either up or low transitions.

Code:

-- Libraries -------------------------------------------------------------------

--! Main library

library ieee;

--! std logic components

use ieee.std_logic_1164.all;

-- Entity ----------------------------------------------------------------------

--! bouncer signals

entity entity_debounce is

generic

(

--! Stores the maximum hysteresis value.

max : natural;

--! Disables the up counting hysteresis when true

hystup_dis : boolean;

--! Disables the down counting hysteresis when true

hystdown_dis : boolean

);

port

(

--! Clock signal. Rising edge triggers the counter.

clk : in std_logic;

--! Input signal that needs debouncing

input : in std_logic;

--! clean, debounced output

output : out std_logic

);

end entity_debounce;

-- Architecture ----------------------------------------------------------------

--! Debounce hysteresis mechanism implementation

architecture arch_debounce of entity_debounce is

--! internal key memory state

signal key : std_logic := input;

begin

process_debounce : process(clk)

--! Hysteresis counter

variable cnt : natural := 0;

begin

if (rising_edge(clk)) then

if (input = '1') then

if ((cnt < max) and (hystup_dis = false)) then

cnt := cnt + 1;

elsif (key = '0') then

key <= '1';

cnt := max;

end if;

else

if ((cnt > 0) and (hystdown_dis = false)) then

cnt := cnt - 1;

elsif (key = '1') then

key <= '0';

cnt := 0;

end if;

end if;

end if;

end process;

output <= key;

end arch_debounce;.

.

.

In the top vhd file:

Code:

--! Debouncer instance 20 ms hysteresis debounce time

debounce_ledbtn20ms : entity_debounce

generic map

(

max => 656,

hystup_dis => true,

hystdown_dis => false

)

port map

(

clk => clk_32k,

input => pin_ledbtn,

output => pins_led(0)

);On the scope one can see that 1st transition is not correct, since falling edge should have debounce added (hystdown_dis => false). There should never be debounce added on rising edges and that is OK (hystup_dis => true).

I would appreciate all help.

Last edited: