rmanalo

Advanced Member level 4

- Joined

- Feb 8, 2017

- Messages

- 107

- Helped

- 16

- Reputation

- 32

- Reaction score

- 16

- Trophy points

- 18

- Location

- Philippines

- Activity points

- 979

Hello Everyone,

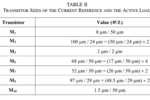

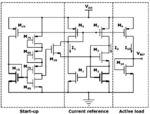

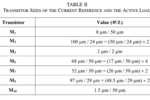

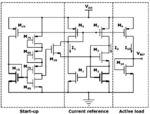

I'm trying to simulate the Design from the paper in [1] using HSPICE. The attached are the sizes and schematic of the design.

In HSPICE the max limit for L is 20um but the design uses 50um. How do I simulate this in HSPICE?

[1] L. Magnelli, et. al., "A 2.6 nW, 0.45 V Temperature Compensated Subthreshold CMOS Voltage Reference," IEEE J. Solid-State Circuits, vol. 46, no. 2, pp.465-474, Feb. 2011.

Best Regards,

rmanalo

I'm trying to simulate the Design from the paper in [1] using HSPICE. The attached are the sizes and schematic of the design.

In HSPICE the max limit for L is 20um but the design uses 50um. How do I simulate this in HSPICE?

[1] L. Magnelli, et. al., "A 2.6 nW, 0.45 V Temperature Compensated Subthreshold CMOS Voltage Reference," IEEE J. Solid-State Circuits, vol. 46, no. 2, pp.465-474, Feb. 2011.

Best Regards,

rmanalo